Academic Background

- Ph.D. in Microelectronics, LIRMM , 1994

- M.Sc. in Computer Science, PPGC‑UFRGS , 1990

- B.S. in Electrical Engineering, EE‑UFRGS , 1987

Professor at PUCRS • School of Technology • PPGCC

Member of: IEEE (Senior) • SBC • SBMicro

CNPq Research Productivity Grant - Level A

PUCRS Researchers Profile

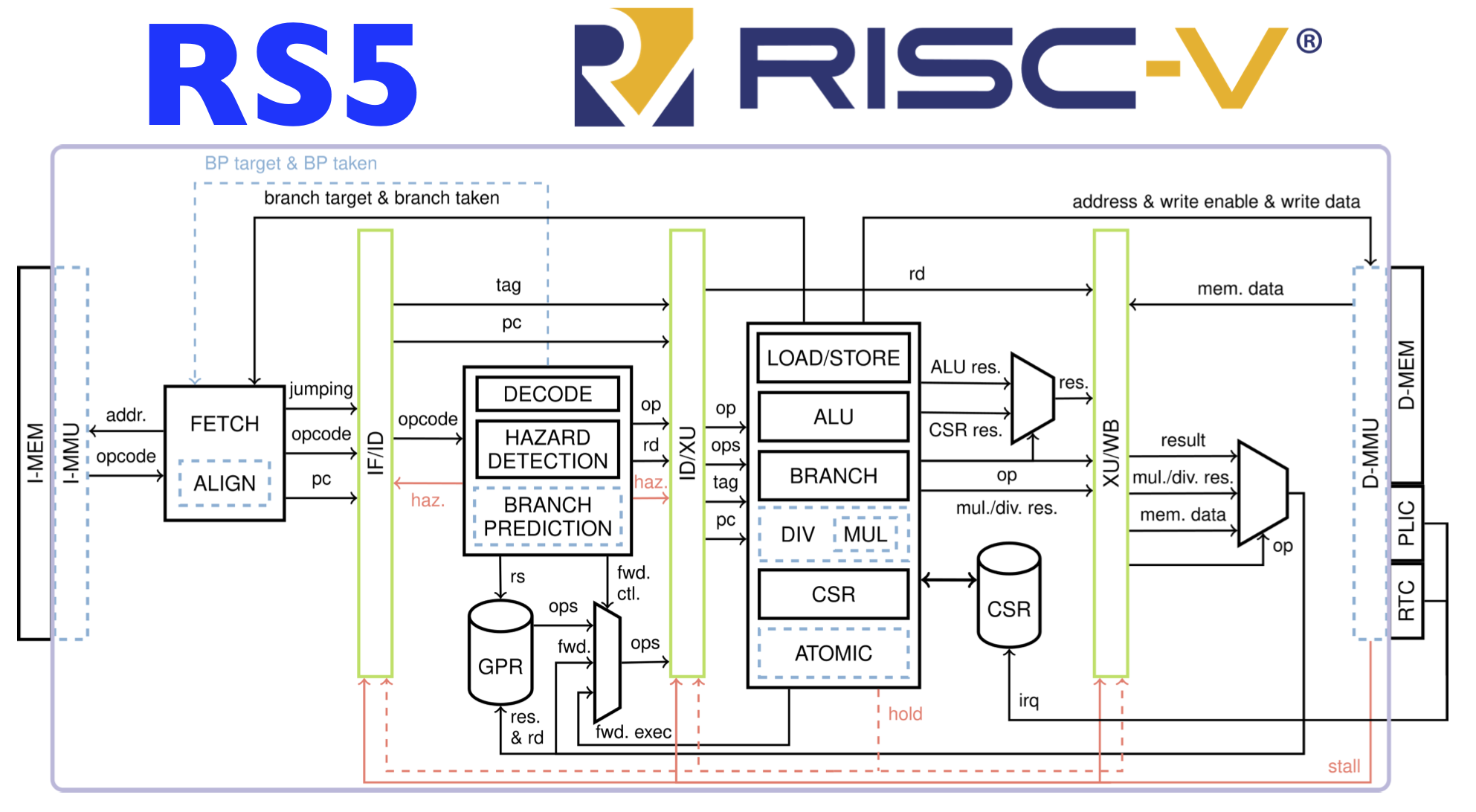

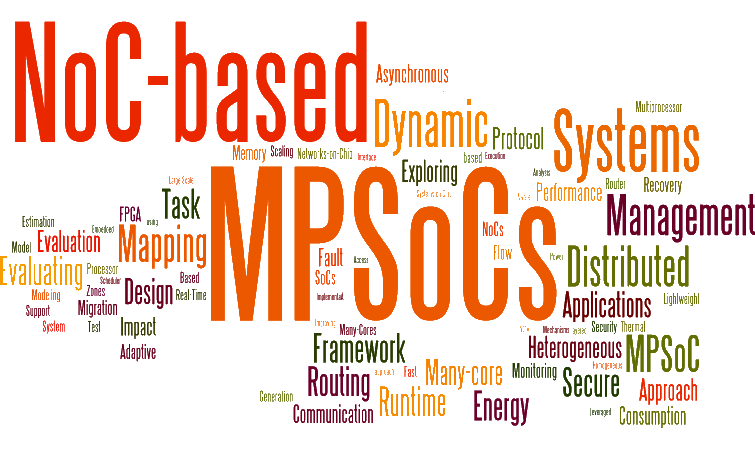

Fernando Moraes received the Electrical Engineering and M.Sc. degrees from UFRGS, Porto Alegre, Brazil, in 1987 and 1990, respectively, and the Ph.D. from LIRMM, France, in 1994 (Très Honorable avec Félicitations du Jury). He is a Full Professor at PUCRS (since 2002) and served as an Invited Professor at Université de Montpellier in 1998, 1999, 2000, and 2017. SBMICRO Financial Director for the period 2024-2026. He has authored 63 peer‑reviewed journal articles and over 280 conference papers on VLSI, many‑cores, NoCs, cryptography, and ML accelerators. He advised 35 M.Sc. and 22 Ph.D. theses. He serves on the program committees of SBCCI, ISVLSI, NoCs, and DATE, and is an Associate Editor of IEEE TCAS‑II (since 2024). Primary interests include microelectronics, FPGAs, reconfigurable architectures, security, NoCs, and MPSoCs.

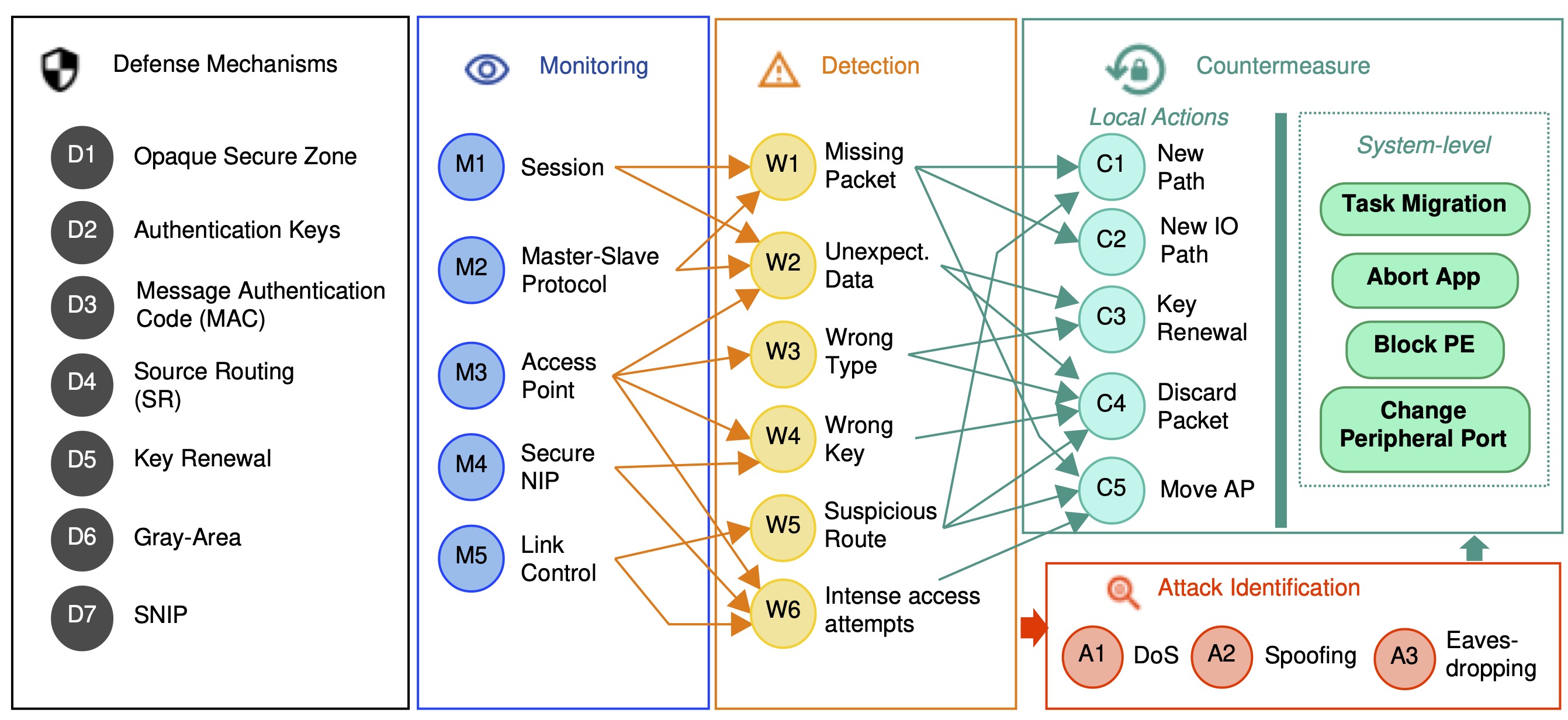

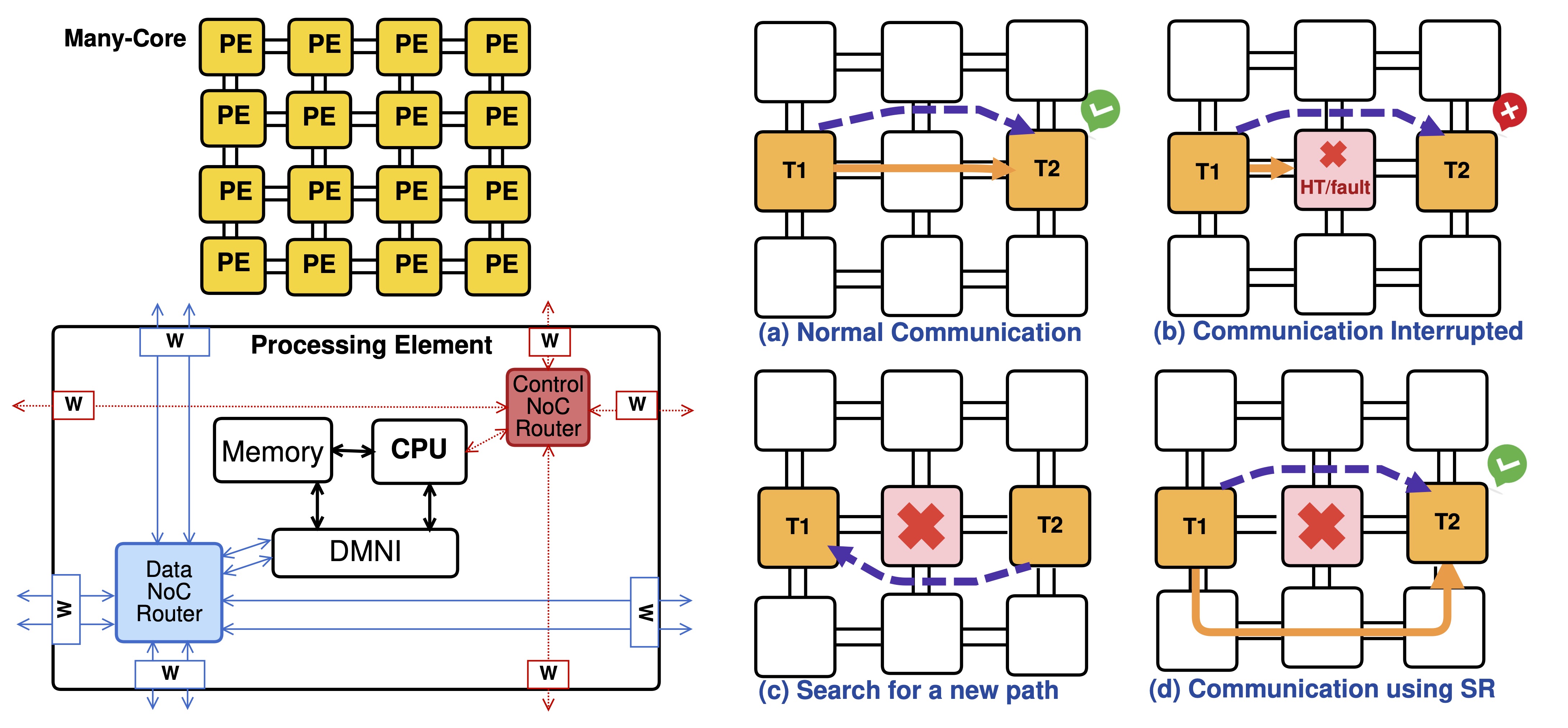

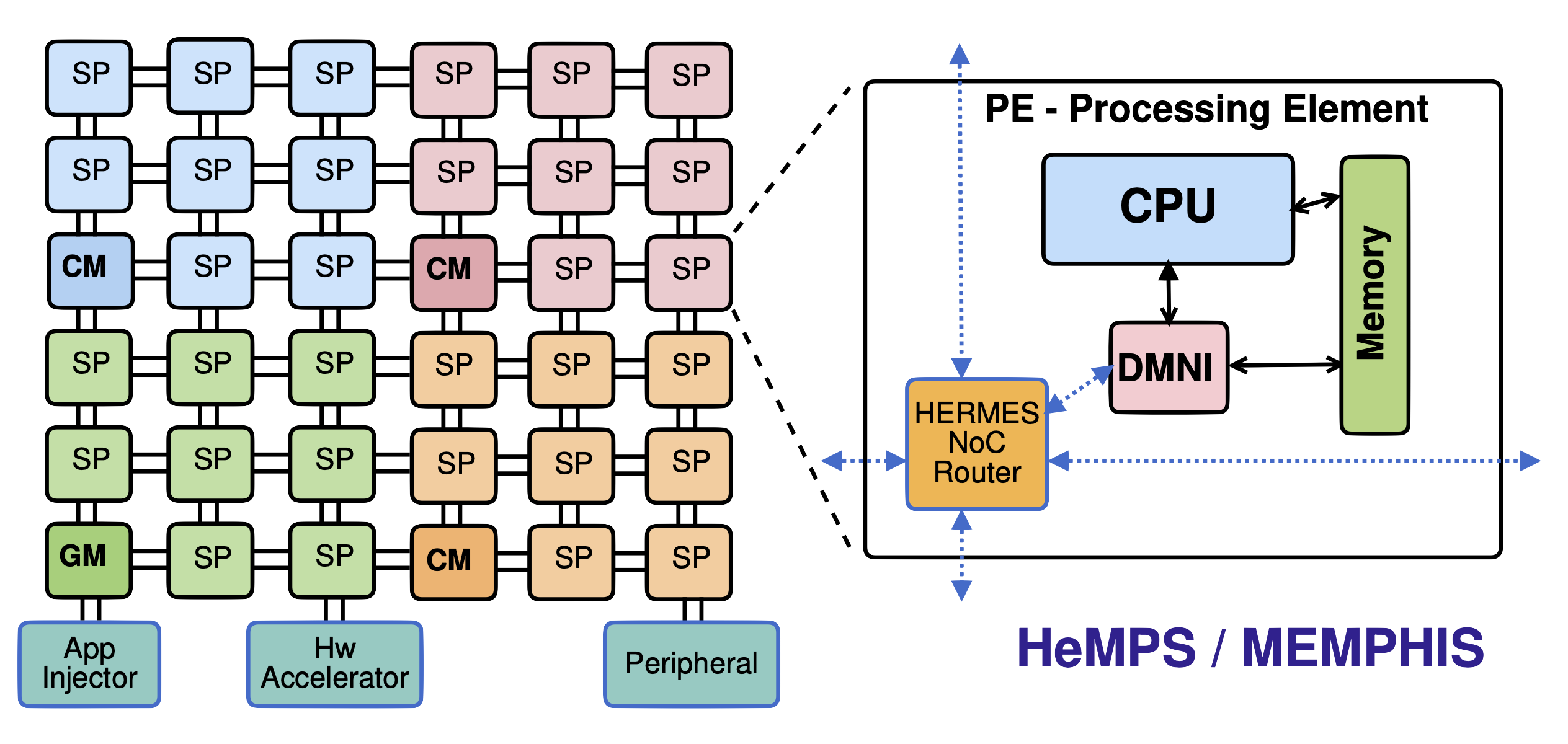

A Comprehensive Framework for Systemic Security Management in NoC‑Based Many-Cores

Detection and Countermeasures of Security Attacks and Faults on NoC‑Based Many‑Cores

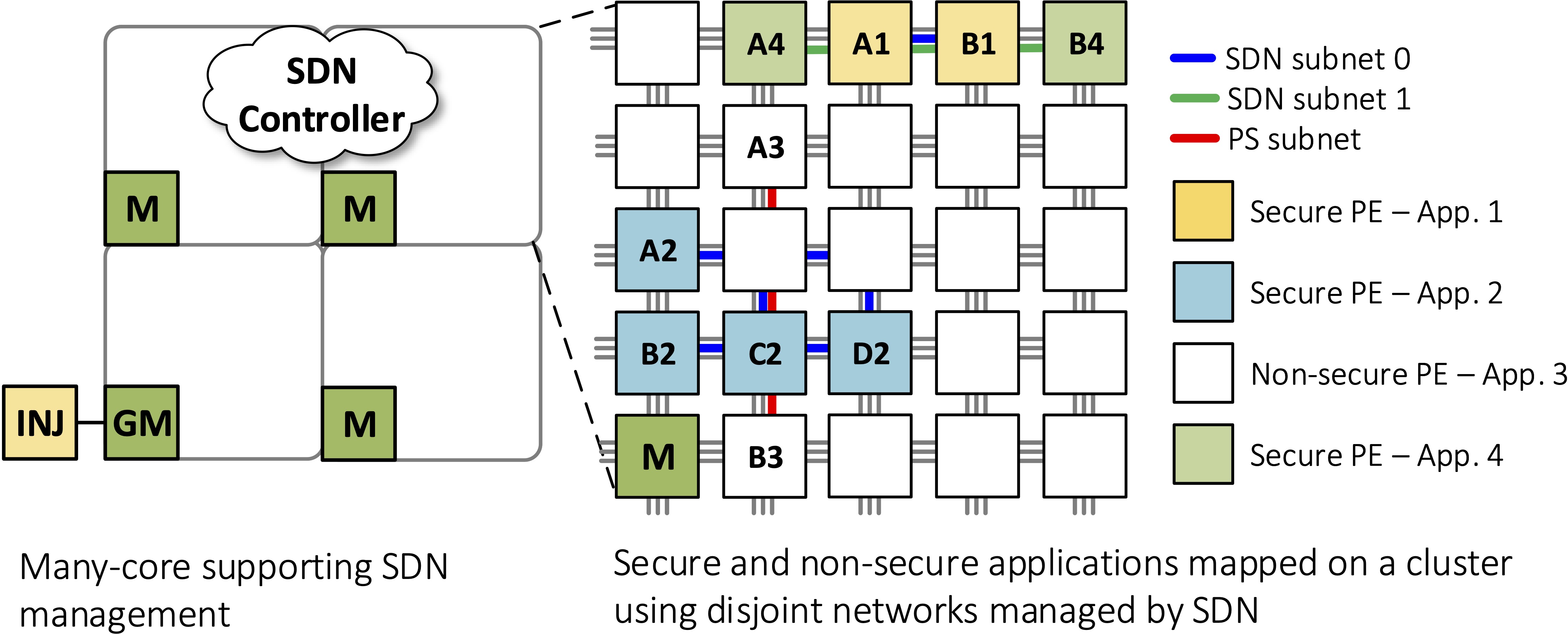

SDN‑Based Secure Application Admission and Execution for Many‑Cores

and best paper

and best paper

Last update: September 17, 2025