# On-Chip Communication Architecture Standards

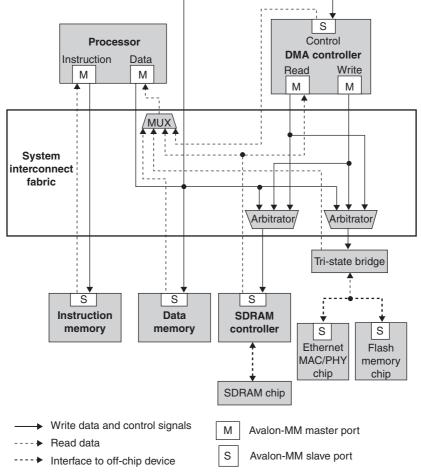

System-on-chip (SoC) designs typically have several different types of components such as processors, memories, custom hardware, peripherals, and external interface IP (intellectual property) blocks that need to communicate with each other. In SoC design houses, some of these components might be designed from scratch, while others are reused from previous designs or procured from external IP vendors. Each of these components has an interface to the outside world consisting of a set of pins that are responsible for sending/receiving addresses, data, and control information to/from other components. The choice of pins at the interface is governed by the particular bus protocol of the communication architecture. In order to seamlessly integrate all these components into an SoC design, it is necessary to have some kind of a standard interface definition for the components. Without a standard interface definition, the component interfaces will not be compatible with the bus architecture implementation, and consequently will not function correctly. In such a scenario, the components will require the design of logic wrappers at their interfaces (more details in Chapter 9) to correctly interface with the bus architecture being used. These logic wrappers, however, require additional area on the chip and can be time consuming to design and verify.

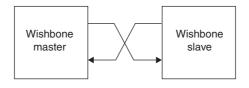

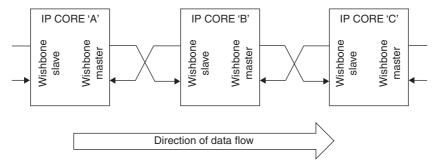

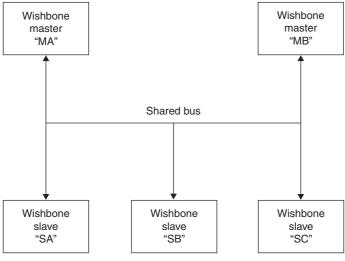

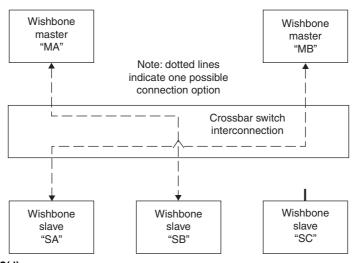

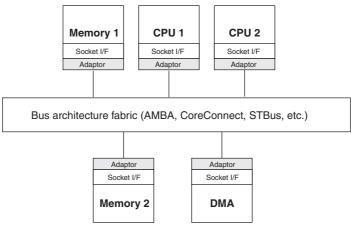

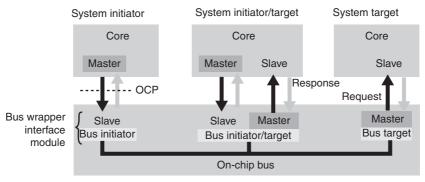

To speed up SoC integration and promote IP reuse over several designs, several bus-based communication architecture standards have emerged over the past several years. A communication architecture standard defines a specific data transfer protocol, which in turn decides the number and functionality of the pins at the interface of the components. Usually, bus-based communication architecture standards define the interface between components and the bus architecture, as well as the bus architecture that implements the data transfer protocol. Many of the bus architecture standards give designers a certain amount of freedom to implement the bus architecture in one of many ways. For instance, most bus-based communication architecture standards give designers freedom to select arbitration policies that are suitable for the specific SoC being designed. Socket-based bus interface standards on the other hand give absolute freedom to a designer, with respect to the choice and implementation of the bus architecture, since they only provide definitions for designing component interfaces. Any proprietary or standard bus architecture implementation can be selected, and components with

socket-based interface definitions can be connected to it using logic adapters. This allows a great deal of flexibility for IP reuse. In this chapter, we present various standards used in SoCs with bus-based communication architectures. Section 3.1 details some commonly used bus-based communication architecture standards. Section 3.2 describes popular socket-based bus interface standards. Finally, we briefly discuss some of the standards for off-chip interconnects in Section 3.3.

## 3.1 STANDARD ON-CHIP BUS-BASED COMMUNICATION ARCHITECTURES

Since the early 1990s, several on-chip bus-based communication architecture standards have been proposed to handle the communication needs of emerging SoC designs. Some of the popular standards include ARM Microcontroller Bus Architecture (AMBA) versions 2.0 [1] and 3.0 [2], IBM CoreConnect [3], STMicroelectronics STBus [4], Sonics SMART Interconnect [5], OpenCores Wishbone [6], and Altera Avalon [7]. The next few sections describe these bus-based communication architecture standards in more detail. Since these standards are constantly evolving, the descriptions of these standards presented here are meant to serve as exemplars, to highlight the capabilities and features required from on-chip communication architectures for supporting diverse SoC application requirements.

#### 3.1.1 AMBA 2.0

AMBA version 2.0 [1] is one of the most widely used on-chip communication standards today. The goal of this standard is to provide a flexible high performance bus architecture specification, that is technology independent, takes up minimal silicon area, and encourages IP reuse across designs. AMBA 2.0 defines three distinct bus standards:

- 1. Advanced bigb performance bus (AHB), which is a high performance bus meant to connect high bandwidth, high clock frequency components such as microprocessors, DMA (Direct Memory Access) controllers, off-chip memory interfaces, and high bandwidth on-chip memory blocks.

- 2. *Advanced system bus (ASB)*, which is a light-weight alternative to the AHB bus, meant to connect high clock frequency components that do not need the advanced protocol features of AHB.

- 3. *Advanced peripheral bus (APB)*, is a low complexity bus optimized for low power operation, and meant for high latency, low bandwidth peripheral components such as timers, UARTs (universal asynchronous receivers/transmitters), user interface (e.g., keyboard) controllers, etc.

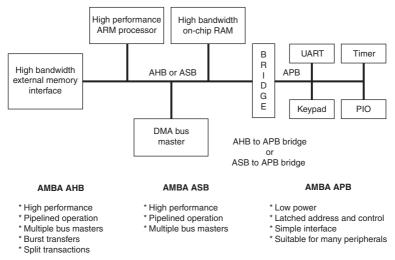

Figure 3.1 shows an example of a typical AMBA-based system, with the buses arranged in a simple hierarchical bus topology (see Chapter 2). The AMBA AHB (or ASB) bus typically acts as a backbone bus that provides a high bandwidth interface between the components involved in a majority of the transfers. The bridge component on the high performance bus is used to interface to the lower bandwidth APB bus, to which most of the low bandwidth peripherals are

FIGURE 3.1

A typical AMBA 2.0 system [1]

Source: ARM Inc.

connected. Note that Fig. 3.1 shows just one of the topology arrangements possible with the AMBA 2.0 buses. Other topology configurations such as single shared bus, multi-layer AHB (or bus matrix) are also possible and will be discussed later in this section. Also note that the AMBA specification [1] is described at the architectural level granularity, and does not provide any information about the electrical characteristics of the bus, which are dependent on the selected manufacturing process technology. Even the timing specifications are only provided in terms of signal behavior at the cycle level—the exact timing requirements depend on the selected complementary metal-oxide semiconductor (CMOS) process technology and frequency of operation. The AMBA specification [1] defines all the signals, transfer modes, structural configuration, and other bus protocol details for the AHB, ASB, and APB buses. Since the specification recommends using the AHB over the ASB for all new designs, and the features of the ASB are simply a subset of the AHB features, we will not present details of the ASB bus. We now describe the specifications of the AHB and APB buses.

## 3.1.1.1 Advanced High Performance Bus

The AHB bus standard describes a high performance bus that supports advanced features for high bandwidth, low latency data transfers. AHB can be used to connect multiple master components, and supports high performance data transfer features such as pipelined operations, burst mode transfers, and split transactions. A single 32-bit address bus is used by the masters to transmit the addresses of the slaves required to complete the read or write data transfer requests. Since the AMBA specification restricts all its on-chip buses to a non-tri-state implementation, the AHB has separate data buses for reads and writes. The data buses have a minimum recommended width of 32 bits, but can have any values ranging through 8, 16, 32, 64, 128, 256, 512, or 1024 bits, depending on application bandwidth requirements,

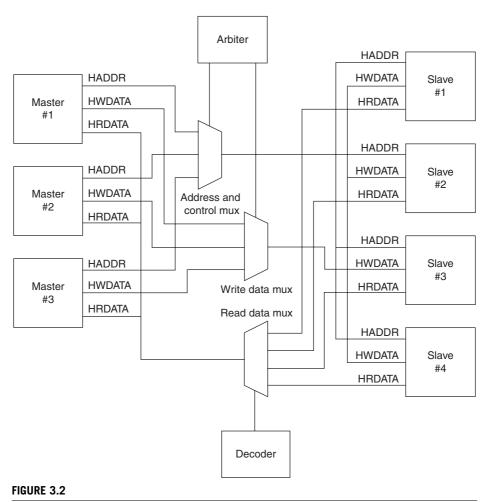

AHB multiplexer interconnection scheme [1] *Source: ARM Inc.*

component interface pin constraints, and the bit width of words accessed from memory modules (e.g., embedded DRAM). Figure 3.2 shows the structure of a simple AHB shared bus with 3 masters and 4 slaves. As can be seen, the AHB makes use of a central multiplexer-based interconnection scheme, along with centralized arbiter and decoder modules to manage data transfers. The masters on the bus drive their address signals (*HADDR*) and control signals (not shown in the figure) whenever they want to perform a data transfer, and the arbiter determines which of the masters will have its address, control, and possibly write data (or *HWDATA*) signals routed (broadcast) to all the slaves on the bus. The decoder is used to decode the destination slave address, select the appropriate slave to receive the data transfer request, and route back response (and possible read data or *HRDATA*) signals to the masters.

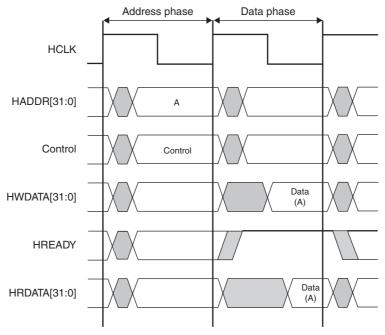

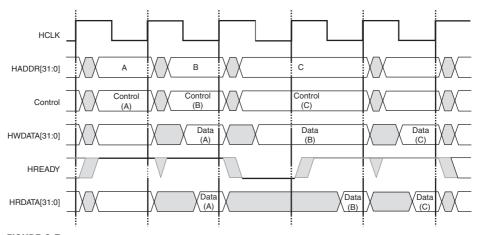

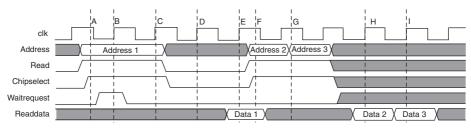

Figure 3.3 shows a basic data transfer on the AHB bus. An AHB transfer consists of an address phase that lasts for a single cycle, and a data phase, that can require

FIGURE 3.3

Basic data transfer on AHB bus [1] *Source: ARM Inc.*

one or more cycles. In the figure, the master drives the address and control signals on the bus after the rising edge of the clock (*HCLK*) in the address phase. The slave samples (i.e., reads) the address and control signals at the next rising edge of the clock, which marks the beginning of the data phase. In the case of a read, the slave drives the appropriate data onto the read data bus (*HRDATA*) in this data phase cycle, followed by the master sampling the data off the bus on the third rising edge of the clock. Otherwise, in the case of a write, the master drives the data onto the write bus (*HWDATA*) in the data phase, followed by the slave sampling the data off the bus on the third rising edge of the clock. Note that Fig. 3.3 shows data on both the read and write buses for illustration purposes only (corresponding to a read or a write, respectively). In practice, the read data bus will be idle on a write, and the write data bus will be idle during a read.

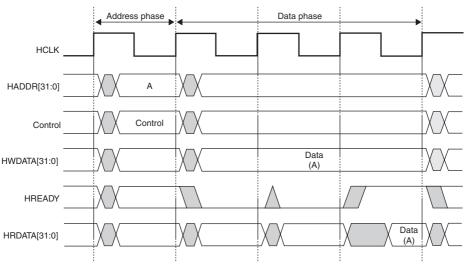

It is possible that the slave can require more than one cycle to provide a response to the master, either because it needs one or more cycles to read the requested data, or to get in a state to write data. In such cases, the slave can introduce wait cycles by lowering the *HREADY* signal to indicate to the master that additional time is required to complete the transaction. Figure 3.4 shows the case for a read (or write) operation, where the slave inserts two wait cycles by lowering the *HREADY* signal for two cycles, before driving the read data onto the read data bus (or sampling the write data from the write data bus). Since the address and data phases of a transfer occur in separate cycles, it is possible to overlap the address phase of one transfer with the data phase of another transfer, in the same clock period. Such

#### FIGURE 3.4

Basic data transfer on AHB bus with slave wait states [1] Source: ARM Inc.

#### FIGURE 3.5

Pipelined data transfers on AHB bus [1] Source: ARM Inc.

a *pipelined* operation of the AHB bus, depicted in Fig. 3.5, allows for high performance operation.

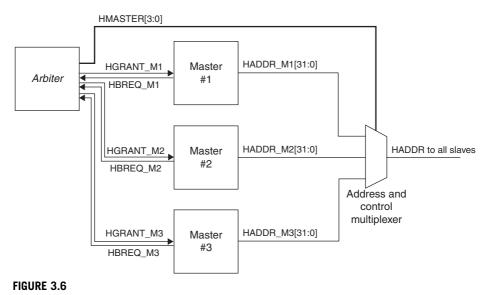

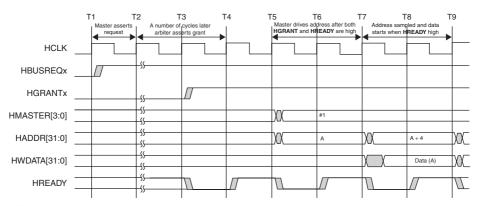

In addition to the address and data phases, an arbitration phase is necessary for all data transfers if there is more than one master connected to a bus. The arbitration phase ensures that only one master gains access to the bus and proceeds with its data transfer at any given point of time. Figure 3.6 shows the centralized arbitration scheme on an AHB bus to which three master components are connected. Whenever a master needs to initiate a read or write data transfer,

Arbitration on AHB bus [1] Source: ARM Inc.

FIGURE 3.7

Cost of arbitration on AHB bus [1] Source: ARM Inc.

it drives the *HBUSREQ* signal to the arbiter, requesting it for access to the AHB bus. The arbiter samples the *HBUSREQ* signals from all the masters and uses its arbitration policy to decide which master gets granted access to the bus access. The AHB specification does not identify a particular arbitration scheme—instead, a designer is given the freedom to implement any suitable scheme depending on the target application latency and bandwidth requirements. Once the arbitration scheme selects a master, the arbiter drives the *HGRANT* signal to the selected master, indicating it has been granted access to the bus and can proceed with its transaction. All the other masters must wait until re-arbitration, after completion of the current data transfer. Figure 3.7 shows an example of how the arbitration

| HBURST[2:0] | Туре   | Description                              |  |

|-------------|--------|------------------------------------------|--|

| 000         | SINGLE | Single transfer                          |  |

| 001         | INCR   | Incrementing burst of unspecified length |  |

| 010         | WRAP4  | 4-beat wrapping burst                    |  |

| 011         | INCR4  | 4-beat incrementing burst                |  |

| 100         | WRAP8  | 8-beat wrapping burst                    |  |

| 101         | INCR8  | 8-beat incrementing burst                |  |

| 110         | WRAP16 | 16-beat wrapping burst                   |  |

| 111         | INCR16 | 16-beat incrementing burst               |  |

#### FIGURE 3.8

Different burst modes on the AHB bus [1]

Source: ARM Inc.

proceeds on an AHB bus: the master asserts the *HBUSREQ* signal to request bus access from the arbiter, which samples the requests at the next rising clock edge, uses its internal arbitration scheme to select a master, and then grants it access to the bus by asserting the *HGRANT* signal. Note that there is typically at least a one cycle overhead for arbitration that can increase to several cycles in the case of a more complex arbitration scheme, or when there are a large number of masters connected to the bus. Such a large overhead for a single data transfer can limit the performance on the bus. To alleviate this overhead, the AHB bus supports burst data transfers that only need to arbitrate once (at the beginning of the transaction) for transferring multiple data items.

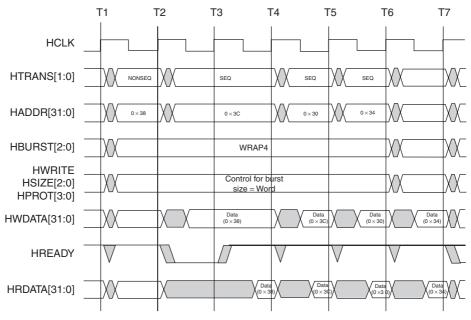

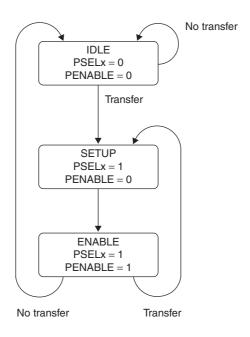

Figure 3.8 shows the different burst modes allowed for the AHB bus. The master uses the HBURST signal to indicate the size of a burst data transfer. Incrementing bursts (INCR, INCR4, INCR8, and INCR16) access sequential locations, and the address of each transfer in the burst is simply an increment of the previous address. Wrapping bursts are similar to incrementing bursts, but if the start address of the data transfer is not aligned to the total number of bytes in the burst, then the address of the transfers in the burst will wrap when the boundary is reached. For instance, a wrapping burst of length 4, transferring word-sized (4 byte) data items will wrap at 16 byte boundaries. So if the start address of a transfer is 0x64h, then the four addresses in the burst will be 0x64h, 0x68h, 0x6Ch, and 0x60h. Figure 3.9 presents an example of a wrapping burst of length 4 (WRAP4). Notice the wait state inserted by the slave (by lowering the HREADY signal) for the first data transfer. Since the burst of word transfers will wrap at 16 byte boundaries, the transfer to address 0x3C is followed by a transfer to address 0x30 h. An incrementing burst of length 4 (INCR4) on the other hand would have continued beyond the 16 byte boundary, and would access the following sequence of addresses: 0x38h, 0x3Ch, 0x40h, and 0x44h.

It is possible for an AHB burst to be interrupted by the arbiter, in case a higher priority master needs to transfer data on the bus. If a master loses access to the bus in the middle of a burst, it must reassert its *HBUSREQ* signal to again arbitrate

FIGURE 3.9

Example of a burst transfer—a wrapping burst of length 4 on the AHB bus [1] Source: ARM Inc.

for access to the bus. Master and slave module AHB interfaces must be designed to correctly handle early burst termination. If a master requires that its burst transfer not be interrupted, it must assert the *HLOCK* signal when requesting the bus from the arbiter, to indicate that the bus needs to be *locked* away from other masters, for the duration of the burst transfer. When the arbiter sees the *HLOCK* signal for a master request, it must ensure that no other master is granted access to the bus once this master is granted access to the bus and its first data transfer has commenced. In addition to *HLOCK*, there are several other control signals used during data transfers, such as:

- *HWRITE*: A 1-bit signal generated by the master that indicates the transfer direction—a write when it is high, or a read when it is low.

- HSIZE: A 3-bit signal generated by the master that indicates the size of the data transfer. There are 8 possible allowed values for data transfer size ranging from 8 bits (000) to 1024 bits (111). This signal is particularly useful if the size of data being transmitted on the bus is smaller than the bus width.

- HTRANS: A 2-bit signal generated by a master to indicate the type of a transaction. There are four types of transfers possible in AHB: (i) NONSEQ, which is usually a single transfer or the first transfer in a burst, (ii) SEQ, which specifies the remaining transfers in a burst, (iii) IDLE, which indicates that no data transfer is required and is generally used when a master is granted access to the bus, but does not need to transfer any data, and (iv) BUSY, which indicates that the master is continuing with a burst transfer, but the

- next transfer cannot take place immediately (e.g., when the master needs to process a read data for multiple cycles before being ready to receive the next data item in the burst; or when a write data in a burst takes multiple cycles to be generated).

- HRESP: A 2-bit signal generated by the slave that specifies the status of a data transfer. If the data transfer completes successfully, an OKAY response is returned on these signals. Otherwise, if an error occurs (e.g., an attempt to write to a ROM region), an ERROR response is returned. The master can choose to continue a burst transfer if an error occurs in the middle of the burst and rectify the error afterward, or it may decide to cancel the remaining transfers in the burst and handle the error immediately. The SPLIT and RETRY responses are used by slaves to free up the AHB bus when they are unable to provide the requested data immediately. The difference between these two responses is that when an arbiter sees a RETRY response, it will continue to use the normal priority scheme and grant access to the bus to higher priority masters, as usual; whereas on a SPLIT response, the arbiter adjusts the priority scheme and allows any other requesting master (even one with a lower priority) to gain access to the bus. To complete a SPLIT transfer, the slave must inform the arbiter when it has the data available.

- HPROT: A 4-bit protection signal that provides additional information about a data transfer. It is typically used by a component requiring some level of protection control, and can be used to specify, for instance, if the transfer is an opcode (OPC) fetch or a data access. Other possible uses include indications for a privileged mode access or a user mode access, and specifying if a transfer is bufferable or cacheable.

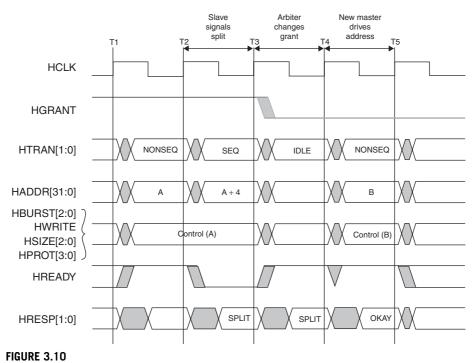

As mentioned above, a SPLIT transfer enables a slave to free up access to a bus, if it believes that the data requested from it (by the master) will not be available for several cycles. In such a scenario, the slave records the ID of the master from which the request initiated (to restart the transfer again at a later time) and asserts an HSPLIT signal to the arbiter. The arbiter then masks (i.e., ignores) requests from the master that was SPLIT, and grants other masters access to the bus. This process is shown in Fig. 3.10, where a SPLIT on the second cycle causes the arbiter to grant bus access to another master. When the slave is ready to complete the transfer, it signals the arbiter and sends the ID of the master that was involved in the split transfer. The arbiter unmasks the master, and eventually grants the master access to the bus, to complete the data transfer. The entire process is transparent to the masters making the request. Thus SPLIT transfers allow the time that would have otherwise been spent waiting for the data from the slave, to be utilized in completing another transfer, which enables better utilization of the bus. Note that an AHB master can only have a single outstanding transaction at any given time. If more than one outstanding transaction needs to be handled by a master component, it requires an additional set of request and grant signals for each such outstanding transaction. Both SPLIT and RETRY transfers can cause bus deadlocks, and therefore care must be taken while implementing them.

SPLIT transfer on the AHB bus [1] Source: ARM Inc.

## AHB Bus Matrix Topology

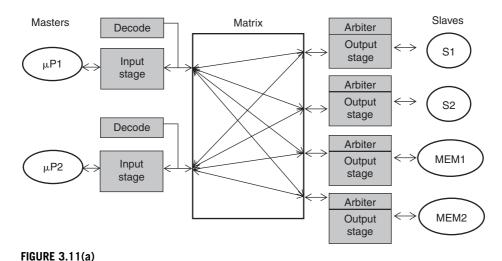

In addition to the basic hierarchical bus topology, where an AHB bus uses a bridge to interface with an APB bus, AHB bus-based communication architectures can have other topologies as well, such as a hierarchical bus topology with multiple AHB (and APB) buses interfacing with each other through bridges. For SoC designs that require very high bandwidths and require multiple concurrent data transfers, the hierarchical bus architecture may be insufficient. For such designs, an AHB multi-layer bus matrix [8] topology offers a more suitable communication infrastructure. Figure 3.11(a) shows an example of a 2 master, 4 slave AHB full bus matrix topology, that has multiple buses in parallel, to support concurrent data transfers and high bandwidths. The Input Stage is used to handle interrupted bursts, and to register and hold incoming transfers from masters if the destination slaves cannot accept them immediately. The Decoder generates select signals for slaves, and also selects which control and read data inputs received from slaves are to be sent to the master. The Output Stage selects the address, control and write data to send to a slave. It calls the Arbiter component, which uses an arbitration scheme to select the master that gets to access a slave, if there are simultaneous requests from several masters. Unlike in traditional hierarchical shared bus architectures, arbitration in a bus matrix is not centralized, but distributed so that every slave has its own arbitration. One drawback of the full bus matrix scheme is

An example of a 2 master, 4 slave AHB: full bus matrix topology

Partial bus matrix topology

that it connects every r

that it connects every master to every slave in the system, resulting in a very large number of buses (and consequently wires and bus logic components). Such a configuration, therefore, achieves high performance at the cost of high power consumption and a larger area footprint. For systems that have less stringent performance requirements, a partial AHB bus matrix [8, 9] topology can be used. Figure 3.11(b) shows a partial AHB bus matrix configuration that clusters components onto shared buses, to reduce the number of buses in the matrix. This partial matrix configuration offers less potential bandwidth due to the likelihood of data traffic conflicts on the shared buses, when compared to the full bus matrix. However, the partial matrix configuration consumes less power and takes up a smaller chip area, which is a desirable characteristic for communication architectures. Pasricha et al. [10] showed how a full AHB bus matrix can be reduced to a

FIGURE 3.12

State diagram representing activity of the APB bus [1] *Source: ARM Inc.*

partial bus matrix topology for a multiprocessor system-on-chip (MPSoC) design, by optimally reducing the number of buses while still meeting all application performance constraints. This methodology is described in more detail in Chapter 6.

## 3.1.1.2 Advanced Peripheral Bus

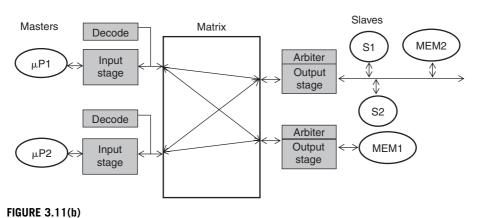

The APB bus standard defines a bus that is optimized for reduced interface complexity and low power consumption. This bus is meant to interface with the AHB (via a bridge), connecting low bandwidth (or high latency) peripheral components that do not require the advanced features of high performance buses such as the AHB. The APB allows only non-pipelined data transfers, and has only a single master—the bridge that connects the AHB bus to the APB bus. Typically, the APB bus operates at a much lower clock frequency (which helps reduce power consumption) and has a smaller bus width, compared to the AHB bus. Figure 3.12 depicts a state diagram that represents the activity on an APB bus. The IDLE state is the default state, in which the APB bus remains when there are no transfer requests from the AHB bus. When a transfer request arrives from the AHB bus via the AHB-APB bridge, the APB bus moves to the SETUP state and asserts the appropriate slave select signal to select the slave on the APB bus that is required to participate in the transfer. The APB bus remains in the SETUP state for one cycle, and this time is spent in decoding the address of the destination peripheral component. The APB bus moves to the ENABLE state on the next rising edge of the clock and asserts the *PENABLE* signal to indicate that the transfer is ready to be performed. This state also typically lasts for one cycle, after which it can go back

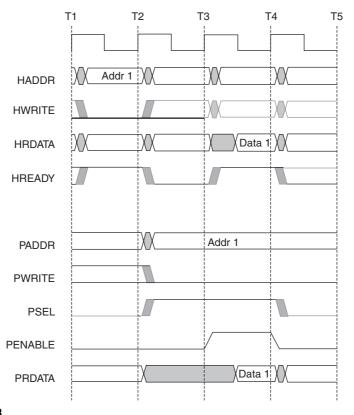

FIGURE 3.13

Read data request from the AHB to the APB bus [1] Source: ARM Inc.

to the *SETUP* stage if another transfer follows the current transfer or to the *IDLE* state if no further transfers are required.

Figure 3.13 illustrates a read request as it propagates from the AHB to the APB bus. The top four signals belong to the AHB bus while the four signals at the bottom belong to the APB bus. The master component on the AHB bus drives the address and control signals onto the AHB bus in the first cycle. These are sampled by the AHB-APB bridge component on the rising edge of the next clock cycle (T2). Since the transfer is intended for the APB bus, the appropriate select signal (*PSEL*) is asserted and the APB bus transitions from the *IDLE* state to the *SETUP* state in cycle T2. This is followed by the *ENABLE* state in cycle T3, in which the slave receives the request and returns the read data. The returned data can usually be directly routed back to the master on the AHB bus, where it will be sampled off the bus at the next rising clock edge (T4). However, for high performance systems, the returned data can be first registered at the bridge, and then driven to the appropriate master in the following cycle. While this approach requires an extra cycle, it can allow the AHB bus to operate at a much higher clock frequency, which allows an overall improvement in system performance. Figure 3.14

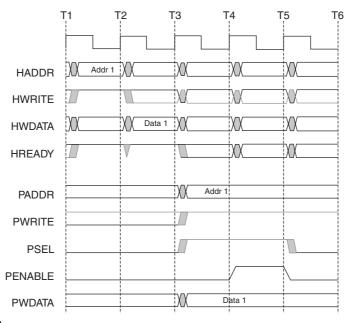

FIGURE 3.14

Write data request from the AHB to the APB bus [1] Source: ARM Inc.

shows a similar scenario, for a write transfer on the APB bus. The bridge samples the address, control, and data signals from the master, holding these values for the duration of the write transfer on the APB bus (as it switches through the *SETUP* and *ENABLE* states).

#### 3.1.2 AMBA 3.0

The AMBA 3.0 bus architecture specification [2] introduces the Advanced eXensible Interface (AXI) bus that extends the AHB bus with advanced features to support the next generation of high performance MPSoC designs. The goals of the AXI bus protocol include supporting high frequency operation without using complex bridges, flexibility in meeting the interface, and performance requirements of a diverse set of components, and backward compatibility with AMBA 2.0 AHB and APB interfaces. We now look at the AXI specification in more detail (Figure 3.15).

#### 3.1.2.1 Advanced Exensible Interface

The AXI bus standard proposes a burst-based, pipelined data transfer bus, similar to the AHB bus, but with additional advanced features and enhancements. The main features of AXI and its differences with the AHB standard are presented in Table 3.1, and elaborated in more detail below.

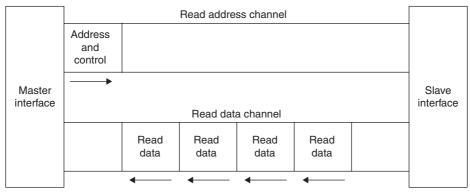

The AXI specification describes a high level channel-based architecture for communicating between masters and slaves on a bus. Five separate channels are defined: *read address*, *read data*, *write address*, *write data*, and *write response*.

FIGURE 3.15(a)

AMBA AXI channel architecture: read address and read data channels

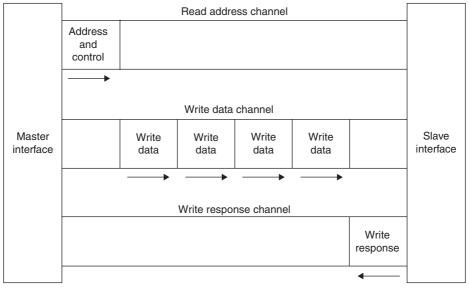

**FIGURE 3.15(b)**

Write address, write data, and write response channels [2] Source: ARM Inc.

Just like for the data bus in AHB, the data channel width in AXI can range from 8 to 1024 bits. The read channels are shown in Fig. 3.15(a). The address and control information for a read transfer is sent by the master on the read channel, while the read data and response information from the slave is received on the read data channel. Figure 3.15(b) shows the write data channels. The address and control information for a write transfer is sent on the write address channel, while the write data is transmitted on the write data channel. A one byte strobe signal is

| Table 3.1 Contrasting features of AXI and AHB                                                                                                                               |                                                                                                          |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|

| AMBA 3.0 AXI                                                                                                                                                                | AMBA 2.0 AHB                                                                                             |  |  |  |

| Channel-based specification, with five separate channels for read address, read data, write address, write data, and write response enabling flexibility in implementation. | Explicit bus-based specification, with single shared address bus and separate read and write data buses. |  |  |  |

| Burst mode requires transmitting address of only first data item on the bus.                                                                                                | Requires transmitting address of every data item transmitted on the bus.                                 |  |  |  |

| OO transaction completion provides native support for multiple, outstanding transactions.                                                                                   | Simpler SPLIT transaction scheme provides limited and rudimentary outstanding transaction completion.    |  |  |  |

| Fixed burst mode for memory mapped I/O peripherals.                                                                                                                         | No fixed burst mode.                                                                                     |  |  |  |

| Exclusive data access (semaphore operation) support.                                                                                                                        | No exclusive access support.                                                                             |  |  |  |

| Advanced security and cache hint support.                                                                                                                                   | Simple protection and cache hint support.                                                                |  |  |  |

| Register slice support for timing isolation.                                                                                                                                | No inherent support for timing isolation.                                                                |  |  |  |

| Native low-power clock control interface.                                                                                                                                   | No low-power interface.                                                                                  |  |  |  |

| Default bus matrix topology support.                                                                                                                                        | Default hierarchical bus topology support.                                                               |  |  |  |

included for every 8 bits of write data, to indicate which bytes of the data bus are valid. This is useful for cases where there is a mismatch between the size of the data being transferred and the data bus width. A separate write response channel provides the slave a means to respond to write transactions. A write completion signal occurs once for every burst (and not for every data transfer) to indicate the status of the write at the slave. The five separate channels provide implementation flexibility to a designer and can be implemented in any one of three ways:

- Shared address bus and shared data buses (SASD): A single shared address

bus is coupled with a bidirectional data bus that handles both reads and

writes. Such a configuration is typically useful for smaller, low complexity

embedded systems.

- 2. Shared address bus and multiple data buses (SAMD): A single shared address bus is coupled with separate, unidirectional read and write data buses. Since the address bus bandwidth is typically less than that of the data buses (as only one address needs to be sent for a burst data transfer), interconnect complexity can be reduced while still maintaining performance, by using a shared address bus.

AMBA 3.0 AXI bus

3. *Multiple address buses, multiple data buses (MAMD)*: A separate address bus for reads and writes is coupled with separate read and write data buses. This configuration has the largest interconnect complexity, but also the best performance of the three implementation alternatives.

The *MAMD* mode in particular allows multiple concurrent read and write transactions to occur independent of each other, which can be very useful for high performance SoC designs. In contrast, AHB only explicitly supports the *SAMD* implementation mode.

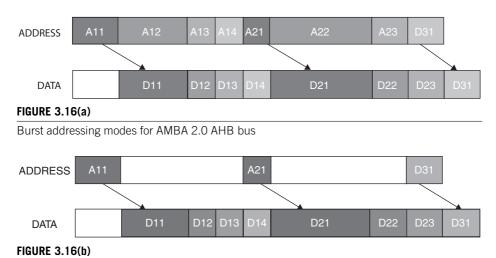

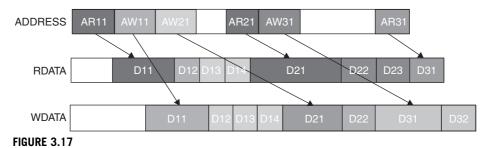

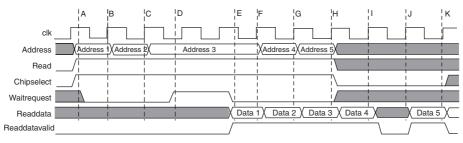

One significant difference between AXI and AHB is the way addressing is handled during burst data transfers. In AHB, every data transfer in a burst requires an address to be transmitted on the address bus. In contrast, AXI requires the address of only the first data item in the burst to be transmitted. Figure 3.16(a) shows burst data transfers on an AHB bus that require an address for every data item transmitted. Contrast this with the same scenario on an AXI bus, shown in Fig. 3.16(b), where only the address of the first data item in a burst is transmitted. It is the responsibility of the slave to calculate the address of the subsequent transfers in the burst. Because only a single address is transmitted per burst, the address buses in AXI are freed up to handle other transactions. Figure 3.17 shows how read and write transactions can occur simultaneously in an SAMD implementation of AXI, because the address bus is freed up during a burst. The AHB in contrast must wait for a burst to complete before initiating another transfer, which results in under-utilization of its data buses. Another enhancement in AXI, compared to AHB, comes in the form of support for an additional burst type. AXI not only supports all the incrementing and wrapping burst types present in AHB, but also an additional fixed burst mode. In this mode, the address of every data item transferred in a burst remains the same. This burst type is very useful for repeated accesses to the same location, such as for data transfers with an I/O peripheral FIFO (first-in-first-out).

Better utilization of data buses in AXI

Another important AXI feature is its support for out-of-order (OO) transaction completion which is an advanced feature that maximizes data throughput and improves system efficiency. AXI masters have the ability to issue multiple outstanding addresses, which means that transaction addresses can be issued without waiting for earlier transactions to complete. This is accomplished by assigned IDs to read and write transactions issued by the masters. The AXI specification lays down certain guidelines to govern the ordering of transactions. Transactions from different masters have no ordering restrictions and can complete in any order. Transactions from the same master but with different ID values can complete in any order. However, a sequence of write transactions with the same ID value must complete in the same order in which the master issued them. For a sequence of read transactions with the same ID value, two possible scenarios exist: (i) reads with the same ID value are from the same slave, in which case it is the responsibility of the slave to ensure that the read data returns in the same order in which the addresses are received; and (ii) reads with the same ID value are from different slaves, in which case the AXI bus logic must ensure that the read data returns in the same order that the master issued the addresses in.

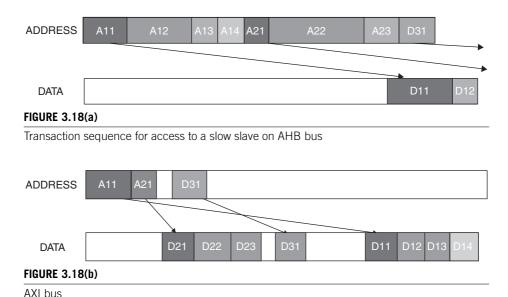

The ability to finish transactions OO allows completion of transactions to faster regions of a memory (or peripheral), without waiting for earlier transactions to slower regions. This feature reduces the effect of transaction latency and improves system performance. Figure 3.18 shows a comparison between AHB and AXI for a scenario where a master must access a slow (i.e., high latency) slave. Figure 3.18(a) shows how an access to a slow slave in AHB holds up the master and the bus till the slave is ready to return the data. Note that using SPLIT transactions on AHB can free up the bus, but not the master, which is still stalled. In contrast, in the AXI case, as shown in Fig. 3.18(b), the master need not wait to get the data back from the slave before issuing other transactions. Both the bus and the master are freed up in AXI, which allows better performance, higher efficiency, and greater bus utilization. Although theoretically any number of transactions can be reordered on the AXI bus, a practical limit is placed by the read/write data reordering depth at the slave interfaces. The read or write data reordering depth of a slave is the number of addresses pending in the slave that can be reordered. A slave that processes all transactions in order is said to have a data reordering depth of 1. This reordering depth must be specified by the designer for both reads and writes, and involves a trade-off between hardware complexity and parallelism in the system—a larger reordering

depth requires greater hardware complexity, but also improves parallelism and possibly overall system performance. However, there is a limit beyond which increasing the reordering depth for a slave does not improve performance because there is typically a limit to the maximum number of concurrent transfers possible in an application, as shown by Pasricha et al. [11].

Other areas where AXI improves on and differs from the AHB feature set include:

- Semaphore operations: AXI provides support for semaphore type operations using an exclusive access mechanism that does not require the bus to remain locked to a particular master for the duration of the transaction. The support for semaphore type operations in AXI therefore does not affect maximum achievable bandwidth or data access latency. In contrast, AHB does not provide any support for semaphore type operations. An exclusive access on AXI is initiated when a master performs an exclusive read from a slave address location. At some later time, the master attempts to complete the exclusive access by attempting to write to the same location. The exclusive write access is signaled by the slave as successful if no other master has written to the location between the read and write accesses. A slave is required to have additional logic (such as a monitor unit for each exclusive-capable master ID that can access it) if it supports exclusive accesses.

- Cache support: AXI provides support for system level caches and other performance enhancing components with the help of two 4-bit cache hint signals, one for each of the read and write channels. These cache hint signals provide additional information about how the transaction can be processed. While AHB provides support for basic cache hints (with a 2-bit signal) such as if data is bufferable or cacheable, AXI extends this by providing additional

- signals to specify write-through and write-back cache allocation strategies for reads and writes, as well as providing the designer the option of customizing the hint signals for other purposes such as flushing cache and page tables.

- Protection support: AXI utilizes two 3-bit signals, one each for the read and write data channels, to provide protection against illegal transactions. There are three levels of protection possible, each represented by a single bit of the protection signals: (i) normal or privileged access, used by certain masters to indicate their processing mode and to obtain access to special resources in a system, since privileged accesses typically provide greater access within a system, (ii) secure or non-secure accesses, used in systems where a greater degree of differentiation between processing modes is required, and (iii) instruction or data accesses, to indicate if the transaction is an instruction or a data access. In comparison, AHB provides support for normal/privileged accesses and instruction/data accesses, but not for secure/non-secure accesses.

- Low power support: AXI supports an optional set of signals for low power operation. These signals target two classes of peripherals. The first consists of peripherals that require a power-down sequence, and can have their clocks turned off (to save power) only after they enter a low power state. These peripherals require a signal from the system clock controller to determine when to begin the power-down sequence. The second type of peripherals are those that do not require a power-down sequence, and can assert a signal to indicate when it is acceptable to turn off their clock. AXI provides support for both types of signals. In contrast, AHB does not include any signals for low power peripheral operation support.

- Recommended topology: The AXI specification assumes a default bus matrix topology implementation, without any requirement for complex bridges. Such an implementation is in keeping with the advanced feature set of AXI, and is suitable for contemporary high performance designs. However, this does not limit AXI in any way from being used in a hierarchical bus topology, if required. The AHB specification, on the other hand, assumes a default hierarchical bus topology arrangement, involving an AHB bus interfacing with an APB bus via a bridge. This is in keeping with the comparatively less advanced AHB feature set, but does not limit it from being implemented in a bus matrix topology.

- Register slice support: The clock frequency on a bus puts a limit on the length of its bus wires during physical layout. This is because a signal can only travel a finite distance on the chip in a single clock cycle [12]. As the clock frequency of the bus is increased, the clock cycle period (which is the inverse of the clock frequency) is reduced, and the distance that can be traveled by a signal shrinks. In fact, it can take multiple cycles for a signal to travel between the ends of a chip [13] in Deep Submicron (DSM) process technologies. For high performance SoC designs, high clock frequencies on the bus are essential to meet performance constraints. To sustain these high bus clock frequencies and ensure correct operation on long interconnects, AXI proposes using one or more register slices on a bus. These register slices latch signal information coming from the source and then retransmit it toward the destination.

The advantage here is that the signal need only cover the distance between latches in a single clock cycle. Thus, by inserting register slices, timing closure (i.e., ensuring timing requirements of a design are met) becomes relatively easier. Introducing the register slices will of course increase the latency (in terms of number of cycles required) for communicating on the bus. However, the bus can now be operated at a much higher frequency (compared to a bus with no register slices inserted) which can improve overall system performance. AHB, in contrast, does not provide any such means of alleviating the problem of meeting timing for high performance, high frequency systems.

## AXI Bus Matrix Topology

Just like the AHB protocol, AXI can be connected in a bus matrix topology. ARM distributes an AXI configurable interconnect (ACI) IP at the register transfer level (RTL) called *PL300* [30] (recently superseded by the next version—*PL301* [31]) that allows designers to connect several masters and slaves together with a configurable AXI bus matrix fabric. The structure of the AXI bus matrix is somewhat similar to that of the AHB bus matrix described earlier, but differs in its support for additional features of the AXI protocol such as independent control for decoupled read, write, and response channels, and OO transaction completion. Components are connected to the AXI bus matrix using interface routers. Each master is connected to a slave interface router, and each slave is connected to a master interface router. The interface routers are part of the AXI bus matrix fabric. These routers essentially consist of multiplexing and de-multiplexing elements to ensure appropriate connectivity with other components connected to the bus matrix. The select signal for each router is generated from a control block that is unique for each channel and interface. The control blocks store the routing information necessary to enforce the ordering constraints within the AXI protocol, and consist of arbiters, decoders, content addressable buffers (CABs), and FIFO elements. The bus matrix fabric does not buffer addresses and data—slaves supporting outstanding transactions must provide the required storage locally. Much like in the case of the AHB bus matrix, a full AXI bus matrix (that connects all the masters to all the slaves in a system) supports high bandwidth but can be prohibitively expensive as it requires a very large number of wires and bus logic components. In a lot of cases where a somewhat lower performance is acceptable, a partial AXI bus matrix that clusters components onto shared buses to reduce the number of wires and bus logic components in the matrix may be more suitable. Pasricha et al. [9] showed how a partial AXI bus matrix can be automatically synthesized from a full AXI bus matrix for MPSoC designs. This methodology, which reduces the number of buses in the matrix while satisfying all application performance constraints, is described in more detail in Chapter 6.

#### 3.1.3 IBM CoreConnect

The IBM CoreConnect [3] on-chip communication architecture standard is another popular synchronous bus-based standard that shares many similarities

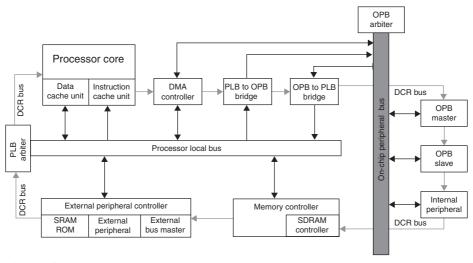

with the AMBA standard. It defines three types of buses: (i) *processor local bus (PLB)*, which is a high performance bus used to connect high speed processor and memory components, (ii) *on-chip peripheral bus (OPB)*, which is used to connect lower performance peripheral components, and (iii) *device control register (DCR)* bus, which is a simple, high latency bus used to access the status and control registers of the PLB and OPB masters. The CoreConnect standard targets a hierarchical bus topology implementation, similar to AMBA 2.0, with the OPB and PLB buses interfacing with each other using a bridge as shown in Fig. 3.19. We now look at the specifications of the PLB, OPB, and DCR buses in more detail.

#### 3.1.3.1 Processor Local Bus

The PLB is a synchronous, high performance bus, similar in many aspects to the AMBA 2.0 AHB, and used to interconnect high performance processor, ASIC, and memory cores. The main features of PLB are summarized below:

- Shared address, separate read and write data buses (*SAMD*).

- Decoupled address, read data, write data buses.

- Support for 32-bit address, 16, 32, 64, and 128-bit data bus widths.

- Dynamic bus sizing—byte, half-word, word, and double-word transfers.

- Up to 16 masters and any number of slaves.

- AND-OR implementation structure.

- Pipelined transfers.

- Variable or fixed length burst transfers.

- Support for 16-64 byte bursts.

- SPLIT transfer support.

FIGURE 3.19

An example of CoreConnect-based SoC design [3]

Reprint Courtesy of International Business Machines Corporation copyright (2001) © International Business Machines Corporation

| Address cycle | Request phase | Transfer<br>phase | Address-acknowledge phase |

|---------------|---------------|-------------------|---------------------------|

|               | Data cycle    | Transfer<br>phase | Data-acknowledge<br>phase |

#### FIGURE 3.20

PLB address and data cycles [3]

Reprint Courtesy of International Business Machines Corporation copyright (2001) © International Business Machines Corporation

- Overlapped read and write transfers (up to 2 transfers per cycle).

- Centralized arbiter.

- Four levels of request priority for each master, programmable secondary arbitration.

- Locked transfer support for atomic accesses.

- Latency timer (to limit a master's tenure on PLB during bursts).

A PLB transaction consists of two cycles: address and data, as shown in Fig. 3.20. The address cycle has three phases: request, transfer, and address acknowledge. A PLB bus transaction is initiated when a master drives its address and control signals, and sends a bus access request to the arbiter, during the request phase. Once the arbiter grants the master access to the bus, the address and control information is sent to the slave in the transfer phase. The address cycle is terminated by the slave latching the address and control information during the acknowledge phase. The data cycle has two phases: transfer and acknowledge. The master drives the write data or samples the read data bus, during the transfer phase. Data acknowledge signaling is required for every data item transmitted on the bus, during the acknowledge phase.

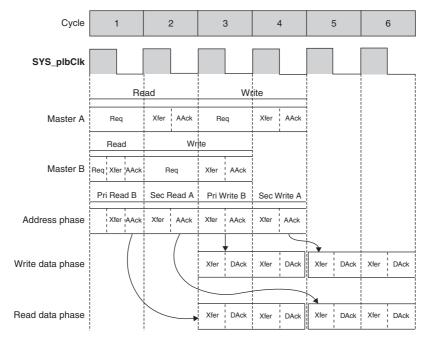

Figure 3.21 shows an example of overlapped transfers on the PLB bus, where two masters perform a single read and a single write transfer each. Due to the decoupled nature of the address, read data, and write data buses, the address cycles can be overlapped with the read or write data cycles, and the read data cycles can be overlapped with the write data cycles. The split bus capability allows for the address and data buses to have different masters at the same time. Support for address pipelining allows a new transfer to begin even before the current transfer has finished. This reduces bus latency by allowing the latency associated with a new transfer request to be overlapped with an ongoing data transfer in the same direction.

A simple write transfer on the PLB bus is shown in Fig. 3.22. A master requests access to the bus for a single write transfer in the first cycle. Due to the slave asserting its wait signal (SI\_wait) to the arbiter, which indicates that the slave is unable to participate in the transaction, the transaction is stalled. The arbiter continues to drive the address and control signals to the slave through this entire period, till it receives the slave address acknowledge (SI\_AddrAck) signal in the fourth cycle. The slave then asserts the write data acknowledge (SI\_wrDAck) and write transfer complete (SI\_wrComp) signals to indicate the end of the transaction.

**FIGURE 3.21**

Example of overlapped PLB transfers [3]

Reprint Courtesy of International Business Machines Corporation copyright (2001) © International Business Machines Corporation

#### FIGURE 3.22

Example of a single write transfer on a PLB bus [3]

Reprint Courtesy of International Business Machines Corporation copyright (2001) © International Business Machines Corporation

Read burst transfer (of length 4) on a PLB bus [3] Reprint Courtesy of International Business Machines Corporation copyright (2001) © International Business Machines Corporation

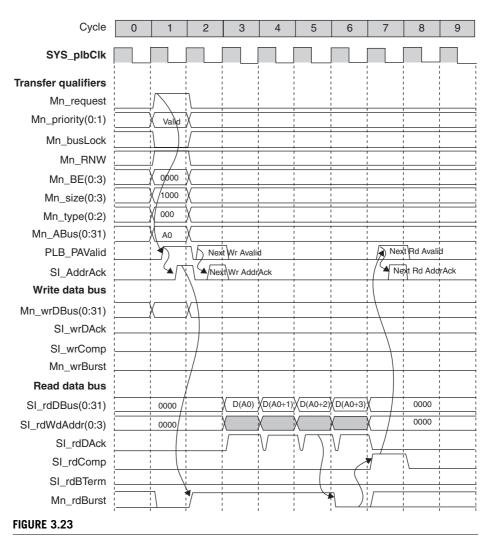

Figure 3.23 illustrates a read burst transfer of length 4 on the PLB bus. The master asserts the request for bus access to the arbiter in the first cycle and is granted access in the same cycle. The slave receives the address and control information and drives the address acknowledge ( $SI\_addrAck$ ) signal to the arbiter in the same cycle. The read data is driven onto the read data bus starting from the third cycle, along with a read data acknowledge ( $SI\_rdDAck$ ) signal for each data item. The slave asserts the read transaction complete signal ( $SI\_rdComp$ ) in the cycle prior to the last read data acknowledge ( $SI\_rdDAck$ ). Note that only the address of the first burst data needs to be transmitted by the master and it is the responsibility of the slave to internally increment the addresses sequentially for each transfer (just like in AMBA 3.0 AXI).

PLB arbiter block diagram [3]

Reprint Courtesy of International Business Machines Corporation copyright (2001) © International Business

Machines Corporation

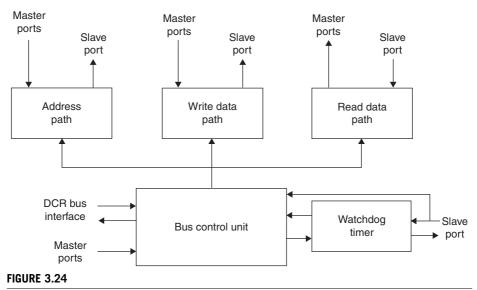

Figure 3.24 shows a block diagram of the PLB arbiter that handles arbitration for up to eight masters. It consists of several components that are described below:

- Bus control unit (BCU): This supports arbitration for masters on the PLB bus. Each master typically drives a 2-bit signal that encodes four priority levels (highest, high, low, lowest), indicating the priority of the request to the arbiter. The arbiter uses this information, in conjunction with the requests from other masters to decide which master to grant the bus access to. In case of a tie, the arbiter provides a choice of using either a fixed (static) priority scheme or a fair, round-robin (RR) priority scheme. The BCU consists of four 32-bit DCRs to control and report its status: (i) PLB arbiter control register (PACR), which is used to program the choice of static or RR priority schemes to be used in case of an arbitration tie, (ii) PLB error address register (PEAR), which contains the address of the access where a bus time-out error occurred, (iii) PLB error status register (PESR), which contains bits to identify time-out errors on PLB bus transfers, the master initiating the transfer, and the type of transfer (read or write), and (iv) PLB revision ID register (PREV), that contains the revision ID of the PLB arbiter core.

- *Address Path Unit:* It contains necessary MUXes to select master address that will be driven to the slaves.

- Read Data Path Unit: It contains necessary steering logic for the read data bus.

- Write Data Path Unit: It contains necessary steering logic for the write data bus

- *Watchdog Timer*: It provides the necessary handshake to complete a transfer, if a master's request times out on the PLB.

To control the maximum latency of a particular application, PLB supports a master latency timer in each master. This latency timer consists of two 8-bit registers: a *Latency Count Register* and a *Latency Counter*. The Latency Count Register is software programmable, with the option of hardwiring the lower 4 bits to ensure a minimum latency of 16 clock cycles. The Latency Counter is used as a clock cycle counter and is not accessible via software code. It is enabled and begins counting the clock cycles during burst data transfers. Once the value of the Latency Counter reaches the value programmed in the Latency Count Register, the master is required to terminate its burst if a request to the bus arrives from another master of equal or higher priority. This timeout mechanism ensures that no master remains parked on the bus for excessive periods of time, and ensures that high priority requests are serviced with low latency.

## 3.1.3.2 On-Chip Peripheral Bus

The OPB is a synchronous bus used to connect high latency peripherals, and alleviate system performance bottlenecks by reducing the capacitive loading on the PLB (since connecting a large number of components on a bus results in high capacitive loading of the bus that increases signal propagation delay and reduces performance). A bridge module is used to interface the OPB bus with a PLB bus. The OPB is more advanced than the simple APB peripheral bus used in AMBA, as indicated by its main features, summarized below:

- Shared address bus, multiple data buses (SAMD).

- Up to a 64-bit address bus width.

- 32- or 64-bit read, write data bus width support.

- Support for multiple masters.

- Bus parking (or locking) for reduced transfer latency.

- Sequential address transfers (burst mode).

- Dynamic bus sizing—byte, half-word, word, and double-word transfers.

- MUX-based (or AND-OR) structural implementation.

- Single cycle data transfer between OPB masters and slaves.

- 16 cycle fixed timeout provided by arbiter, to reduce transfer latency (can be disabled by a slave).

- Slave retry support, to break possible arbitration deadlocks.

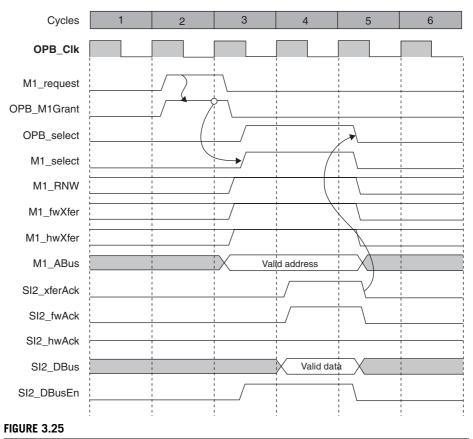

A basic data transfer on an OPB bus is shown in Fig. 3.25. A master requests access to the bus for a read data transfer in the second cycle. The arbiter grants access to the bus, based on its arbitration scheme, and the master subsequently assumes ownership of the bus by asserting the select (M1\_select) signal. The master then drives the address and control signals, which is sampled off the bus by the slave. The slave drives the read data onto the data bus and asserts the transfer acknowledge (S12\_xferAck) signal in the next cycle. The master latches the data off the bus in the following cycle and de-asserts select to end the transaction.

For reducing arbitration latency during multiple transfers, a master can park or lock itself on the OPB bus. The parked master is allowed to access the bus without any delay due to an arbitration cycle, as long as no request is asserted by another master. Like in the case of the PLB, the OPB masters capable of long parked/locked

Basic read data transfer on OPB [3]

Reprint Courtesy of International Business Machines Corporation copyright (2001) © International Business

Machines Corporation

access have Latency Counters to insure a low latency response for requests from other masters. Multiple data transfers to sequential addresses can take advantage of the sequential transfer mode in OPB, which is similar to a burst transfer. Unlike the PLB, a master on the OPB bus must drive addresses for each data item transferred on the bus. OPB also allows the overlapping of a new arbitration request with the final cycle of an ongoing data transfer, to avoid wasting a cycle for bus request and improve performance. The arbiter module is simpler than the PLB arbiter, with only two registers: one for programmable priority and another for controlling bus parking. There is flexibility in choosing either a fixed (static) scheme or a fair, RR scheme. These options are dynamically programmable, allowing for adjustments in priority based on varying traffic profiles or operation modes. The watchdog timer module in the arbiter implements a timeout feature if a slave does not respond to a master request within 16 clock cycles. If a slave must take longer to complete the transfer, it is allowed to inhibit the timer counter in the watchdog.

To alleviate possible deadlock scenarios on the bus, OPB supports the slave retry operation. This allows an OPB slave to assert a retry signal if the slave cannot perform the required bus operation at a particular instant of time. The bus master responds to this signal by immediately terminating its transfer and relinquishing control of the bus for at least one cycle, so that the arbiter can re-arbitrate the bus. This allows the slave a chance to access the OPB in order to resolve the deadlock condition. Note that this mechanism may still be insufficient to guarantee that all possible deadlock conditions will be alleviated. However, the retry operation does provide OPB masters with sufficient information to detect a deadlock situation, and to take corrective action.

OPB, much like PLB, also supports dynamic bus sizing which allows components that have different data interface widths than the OPB data bus to operate seamlessly. When a master transfers data that is wider than the data bus width, it must split the transfer into two or more operations. Similarly, if a data item being transferred has a smaller width than the data bus width, it must be appropriately aligned on a subset of the bus lines. The OPB bus permits byte (8-bit), half-word (16-bit), full-word (32-bit), and double-word (64-bit) sized transfers.

## 3.1.3.3 Device Control Register Bus

The DCR bus is a synchronous bus designed to transfer data between a CPU's general-purpose registers (GPRs) and the device control registers (DCRs) of the slave components in the system. The DCR bus removes device configuration registers from the global memory address map. It allows the lower performance status and control read/write transfers to occur separately, and concurrently with high speed transfers on the PLB and OPB buses, thus improving system response time and overall performance. It is assumed that in a typical SoC environment where DCR master and slave components are operating at different clock frequencies, the slower clock's rising edge always corresponds to the faster clock's rising edge. DCR transactions control the configuration of on-chip peripherals such as interrupt controllers, timers, arbiters, bridges, etc. The main features of the DCR bus are summarized below:

- 10-bit, up to 32-bit address bus.

- 32-bit read and write data buses.

- 4-cycle minimum read or write transfers (extendable by slave or master).

- Slave bus timeout inhibit capability.

- Multi-master arbitration.

- Privileged and non-privileged transfers.

- Daisy-chain (serial) or distributed-OR (parallel) bus topologies.

The DCR bus consists of the address, read and write data buses, and the DCR read, DCR write, master ID, privilege level, timeout wait, and acknowledge signals. Slaves can have privileged registers that can only be accessed by privileged transactions from a master. Any non-privileged transaction meant for a privileged DCR is ignored by the slave and results in a timeout. A typical transfer on the DCR bus is initiated by a master asserting the DCR read or write command signals, and driving the address and appropriate control signals. Slaves decode the command, address, privilege level, and master ID to determine whether to claim the transfer or not.

A slave can claim a transfer by asserting the timeout wait or acknowledge signals. Since requests can time out if a response is not received by the master, a slave that takes longer to complete the transfer must assert the timeout wait signal to prevent a timeout. Asserting the acknowledge signal implies that a write operation is complete, or that read data has been driven onto the read data bus. If no slave responds to the transfer request, a timeout occurs and the master terminates the command.

The DCR bus can be implemented by daisy-chaining the slave components or by creating a distributed-OR structure out of the slave devices. The daisy-chain approach allows for easier chip level wiring while the distributed-OR approach allows for easier chip level timing closure. For the case of the daisy-chain configuration, data moves along the ring-like network connecting all the slave components, and each slave component either passes along the unmodified data input, or puts its data onto its data bus output. In the distributed-OR implementation, each slave directly receives data from the master, and places its data output onto the system OR logic. It is possible for multiple masters to be connected to the DCR bus. In such a case, an arbiter is required to negotiate access to the DCR bus.

### 3.1.4 STMicroelectronics STBus

STMicroelectronics' STBus [4] on-chip communication architecture is an evolutionary on-chip interconnection standard developed for microcontroller consumer applications such as set-top boxes, ATM networks, digital cameras, etc. It is closely related to the VSIA (virtual sockets interface alliance; described in Section 3.2.2) industry interface standard [14] to ease compatibility and integration with third party IP blocks. The STBus standard defines three types of synchronous buses (or bus protocols) having varying levels of complexity in terms of performance and implementation: (i) *Type 1*, which is the simplest bus protocol intended for peripheral register access, (ii) *Type 2*, which is a more complex bus protocol that supports pipelined operations and SPLIT transactions, and (iii) *Type 3*, which is the most advanced bus that implements OO transactions, compound operations, and transaction labeling/hints. These buses are implemented with a MUX-based structure, and can be arranged in either a shared bus, partial crossbar (partial bus matrix), or a full crossbar (full bus matrix) topology. We describe each of these bus protocols in more detail below.

## 3.1.4.1 *Type 1*

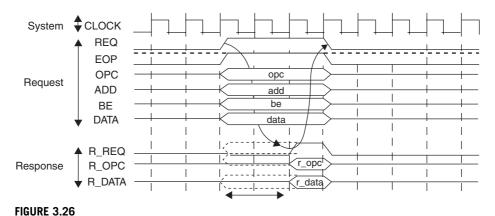

The Type 1 or *peripheral* STBus standard is the simplest protocol in the STBus family that is meant to interconnect components such as general-purpose input/output (GPIO), UARTs, and simple controllers that require medium data-rate communication with the rest of the system. A simple handshaking mechanism is used to ensure correct transmission. Operations on the buses are defined in terms of *OPCs* which define, for instance, whether an operation is a read or a write. The Type 1 bus supports the LOAD (read) and STORE (write) data operations, with an address bus size of 32 bits, and a possible data size of a byte (8-bit), half-word (16-bit), word (32-bit), and double-word (64-bit). Figure 3.26 shows a simple data transfer on the Type 1 bus. The initiator (master) sends a data transfer request (*REQ*) to

Basic data transfer on STBus Type 1 bus [4] Source: STMicroelectronics

the target (slave) by sending the OPC for the transfer (either read or write), the transfer address (ADD), and the byte enable (BE) to specify which bytes in the bus are significant, based on the width of the data involved in the transfer (1-8 bytes). The write data bus (DATA) to send the write data (for a write data transfer). The slave indicates it has received the transfer request by asserting the handshake signal  $(R\_REQ)$ , and then proceeds to return the read data on the read data bus  $(R\_DATA)$  or write data in its address space for a write data transfer. The slave returns an optional response opcode  $(R\_OPC)$  to indicate any errors during the transaction.

The Type 1 bus is similar to the IBM CoreConnect DCR bus, since it is also used to program the internal configuration registers of components connected to the STBus communication architecture. A register decoder block is responsible for performing address decoding, data transfer routing, and arbitration (if more than one master is connected to the bus) for transfers on the Type 1 bus.

## 3.1.4.2 Type 2

The Type 2 or the *basic* STBus standard supports all the Type 1 functionality, and additionally provides support for pipelined operations, SPLIT transactions, compound operations, source labeling, and some priority and labeling/hint information. This bus protocol is targeted at high performance components. The use of SPLIT transactions and pipelined operation improves bus efficiency and performance. The Type 2 standard supports the basic LOAD (read) and STORE (write) operations, with an address bus size of 32 bits and allowed data bus sizes of 8, 16, 32, 64, 128, or 256 bits. Additionally, the Type 2 standard also supports compound operations which are built from one or more primitives. The supported standard compound operations include:

■ *READMODWRITE*: An atomic operation that transfers read data from the slave to the master, but leaves the slave *locked* until a write transfer from the same master completes, replacing the information at the specified address in the slave.

- *SWAP*: An atomic operation that exchanges a data value from the master with the data held in a specified location in a slave.

- *FLUSH*: An operation used to ensure the coherence of main memory while allowing local copies associated with a slave to remain coherent. The operation returns a response when any copies of the data associated with a physical address (which are held by a slave module) are coherent with the actual data at the physical address. The slave may retain a copy of the data.

- *PURGE*: An operation used to ensure the coherence of main memory while ensuring that stale local copies are destroyed. The operation returns a response when any copies of the data associated with a physical address (which are held by a slave module) are coherent with the actual data at the physical address, while removing any copies of the data held by the slave.

- *USER*: This is reserved for user defined operations that can implement useful operations specific to particular applications.

## 3.1.4.3 Type 3

The Type 3 or *advanced* STBus standard supports all Type 1 and Type 2 functionality, but additionally supports packet shaping and OO transaction completion. These features make this bus protocol suitable for very high performance components. The Type 3 supports the same basic and compound operations as the Type 2 standard. Packet shaping allows optimum bandwidth allocation in Type 3 buses, with only the minimum number of clock cycles required to carry out a transaction being used. In Type 1 and Type 2 buses, every request requires a response, which wastes bandwidth. In contrast, a Type 3 requires only a single response from a slave for multiple write data operations by a master, or a single read request from a master for multiple data reads from a slave. Due to this asymmetry between request and response phases, the bandwidth allocation in the Type 3 protocol is optimized compared to the Type 1 and Type 2 protocols. The use of OO transaction completion further reduces latency on the bus since a master waiting for a response from a slave no longer blocks access to other slaves. Transaction IDs associated with data transfers allow the components to have up to 16 transactions in progress.

## 3.1.4.4 STBus Components

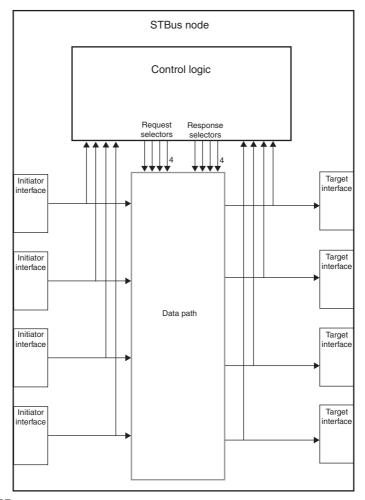

The STBus node shown in Fig. 3.27 is the main component of the STBus on-chip communication architecture. It consists of two main blocks: the *control logic* and the *data path*. The control logic is responsible for the arbitration, decoding, and contains other bus logic required for implementing advanced protocol features (such as OO transaction completion), while the data path represents the topology of the communication architecture, which can be a shared bus, a full crossbar, or a partial crossbar configuration. Master components connect to the initiator interfaces, while slaves connect to the target interfaces of this node architecture.

The control logic is responsible for arbitration, and supports several arbitration schemes which are described below:

- *Fixed priority*: The priorities of the masters are static or hardwired.

- *Variable priority*: The priorities of the masters can be dynamically changed during system operation by writing to special programmable priority registers

#### FIGURE 3.27

Block diagram of STBus node [4] *Source: STMicroelectronics*

in the node. If two or more masters have the same priority value stored in their registers, the master with the higher fixed (hardwired) priority gets preference.

- Least recently used (LRU): Masters are granted access to the bus in the order of the longest time since the last grant. If two or more masters have been waiting for the same amount of time, the master with the higher fixed (hardwired) priority gets preference.

- Latency-based: Each master has a register associated with it containing the maximum allowed latency in clock cycles. If the value is 0, then it needs to have zero cycle latency when a request is received, and such a master must be granted bus access as soon as possible. Each master also has a counter, which is loaded with its maximum latency value each time the master

- makes a request. At every subsequent cycle, the counter is decremented. The arbiter grants bus access to the master having the lowest counter value. If two or more masters have the same counter values, the grant will be given to the master with the higher fixed (hardwired) priority.

- Bandwidth-based: Each master has a register associated with it containing its bandwidth, expressed in terms of clock cycles per fixed period. Each master also has a counter, loaded with a starting value obtained from its bandwidth register. At the beginning of an operation, the counter for the first master (selected based on the hardwired priority) starts decrementing for the entire duration of the time slot allocated to this master. If during this period the first master makes any requests, they are granted. If during this period no master makes any requests, the first master eventually loses its slot, and the next master based on hardwired priority is selected. However, if during this period the first master makes no requests but requests are received from other masters, its counter is stopped and the bus is granted to the next master in order of hardwired priority (whose counter subsequently begins to decrement since it is now using bandwidth). If a master consumes its bandwidth (i.e., its bandwidth counter has reached 0), it cannot be granted bus access again till the end of the fixed time period. This process continues till all masters have consumed their allocated bandwidth, at which point the arbitration process starts again. This scheme is similar to a TDMA/static-priority two level arbitration scheme.

- *STB*: This is a hybrid of the latency-based and variable priority schemes. In its normal state, arbitration proceeds just like in a variable priority scheme. As in the latency-based scheme, masters also have an associated maximum latency register and counter. Each master also has an additional *latency-counter-enable* bit. If this latency-counter-enable bit is set, and the counter value is 0, then a master is said to be in *panic state*. In the case when one or more masters are in a panic state, the normal variable priority scheme is overridden, and the masters in panic state are granted bus access, in the order of highest priority.

- *Message-based*: This is a fixed priority scheme which allows masters having a higher priority and a priority flag set, to interrupt the message transfer on the bus. Note that in the normal fixed priority scheme, a message transfer cannot be interrupted while it is in progress.

From the description of the supported arbitration schemes in STBus, it can be seen that the control unit requires several registers to hold the latency, bandwidth, and/or priority values for the masters in the system. In addition to the node, other components used in the STBus communication architecture include:

- *Size converters*: Components used to allow communication between two STBus IP blocks having different data bus widths.

- *Type converters*: Components used to allow communication between two STBus IPs following different STBus protocol types (e.g., between Type 1 and Type 3).

- Buffer: A FIFO-based component that is used as a retiming stage between two IPs following the Type 2 or Type 3 protocol. A buffer is useful to break

critical paths between components that are far apart from each other on the system floorplan. In this aspect, it is similar to the register slice proposed in AMBA 3.0 AXI.

## 3.1.5 Sonics SMART Interconnect

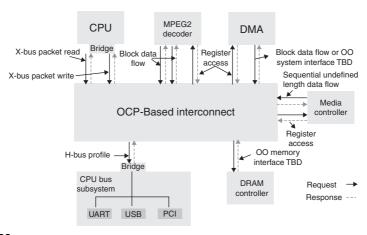

The Sonics SMART Interconnect [5] is another on-chip communication architecture standard designed to ease component interoperability and provide high performance for a wide range of applications. The standard comprises of three synchronous bus-based interconnect specifications which differ in their level of complexity and performance: (i) SonicsMX, which is a high performance interconnect fabric with advanced features; (ii) SonicsLX, which is also a high performance interconnect fabric, but with less advanced features compared to SonicsMX; and (iii) \$3220, which is a peripheral interconnect, designed to connect slower peripheral components. Both SonicsMX and SonicsLX natively support the open core protocol (OCP) version 2.0 [15] wrapper-based interface standard (described in Section 3.2.1). Additionally, components with AMBA 2.0 AHB and AMBA 3.0 AXI natives interfaces can also be plugged into these interconnection fabrics using pre-designed interface bridge logic components. These features are crucial in maximizing reuse of IP cores. Sonics SMART Interconnect provides a highly configurable communication architecture solution for contemporary SoC designs. It is supported by the SonicsStudio development environment [5] that allows automated configuration, data analysis, and performance verification for the communication architecture. We now examine the specifications of the three bus-based interconnect fabrics that make up the Sonics SMART Interconnect, in more detail.

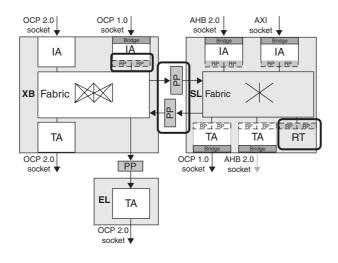

#### 3.1.5.1 SonicsMX

SonicsMX is the third generation of *socket-based* (described in Section 3.2) synchronous interconnect fabrics from Sonics, targeted at high performance, sophisticated SoC applications such as WCDMA/3G wireless headsets, video game consoles, and portable multimedia players. Its main features are summarized below:

- Pipelined, non-blocking, and multi-threaded communication support.

- Split/outstanding transactions for high performance.

- Configurable data bus width: 32, 64, or 128 bits.

- Multiple topology support—shared bus, full crossbar, partial crossbar.

- Socket-based connection support, using native OCP 2.0 [15] interface between components and interconnect.

- Bandwidth and latency-based arbitration schemes to obtain desired quality of service (QoS) for components threads.

- Register points (RPs) for pipelining long interconnects and providing timing isolation.

- Protection mode support.

- Advanced error handling support.

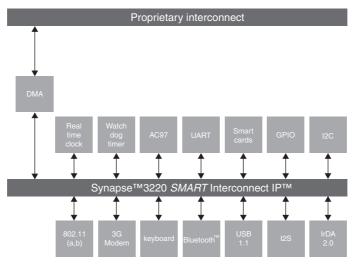

- Fine-grained power management support.