# MICROELETRÔNICA LISTA DE EXERCÍCIOS – UNIDADE 2

Fernando Moraes 04/Junho/2023

# **FLIP-FLOPS**

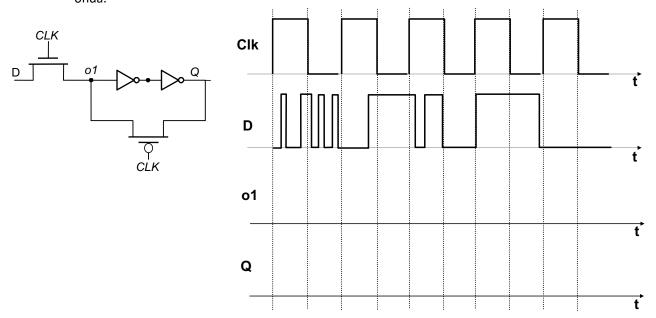

- 1) Para o circuito de memória apresentado abaixo, pede-se:

- a) O circuito é sensível ao nível ou a borda do sinal clk?

- b) Se for sensível à borda do *clk*, é sensível à borda de subida ou descida? Se for ao nível, o circuito é *transparente* ao nível lógico '0' ou ao nível '1'?

- c) Preencha as formas de onda para os sinais internos 'o1' e o sinal de saída 'q'.

- d) Qual a limitação e/ou problema deste circuito? Esta limitação e/ou problema deve aparecer nas formas de

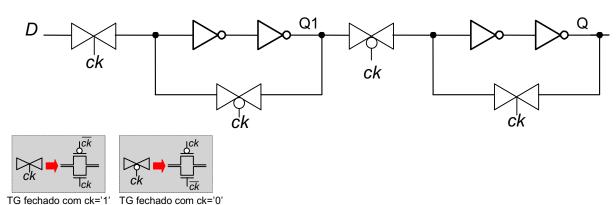

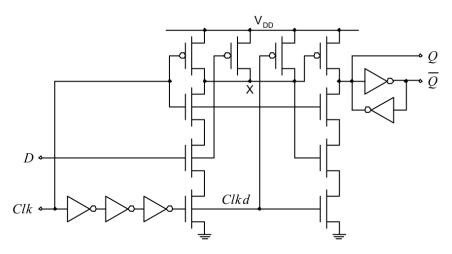

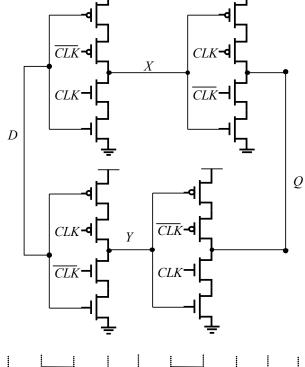

2) Considere o circuito flip-flop D mestre-escravo representado abaixo:

- a) A saída do circuito, sinal Q, é sensível ao nível ou a borda do sinal clk?

b) Se o sinal de saída do circuito (Q) for sensível à borda do clk, é sensível à borda de subida ou descida? Se for ao nível, o circuito é transparente ao nível lógico '0' ou ao nível '1'?

- c) Preencha as formas de onda abaixo para o sinal interno 'Q1' e o sinal de saída 'Q'.

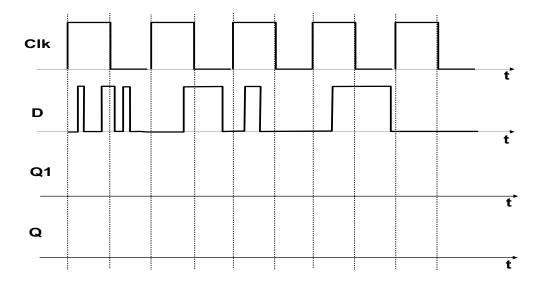

3) Para os circuitos de memória abaixo, com valor inicial do Q1='0' e Q2='0', determine o comportamento de ambos os circuitos, completando os diagramas de tempo abaixo. Não desenhe apenas os diagramas de tempo, explique-os. O "atraso interno" refere-se ao tempo do inversor mais o do circuito de memória.

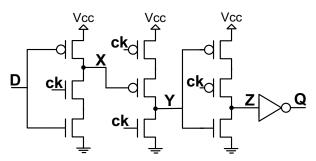

- 4) Considere o circuito flip-flop D mestre-escravo representado abaixo.

- a) Qual o comportamento dos sinais {X,Y,Z} quando o sinal ck é igual ao nível lógico alto ('1')?

- b) Qual o comportamento dos sinais {X,Y,Z} quando o sinal *ck* é igual ao nível lógico baixo ('0')?

- c) A qual borda de *ck* este flip-flop é sensível? Justifique.

Responda a esta questão mostrando o circuito equivalente quando ck=0 ou ck=1. Para os itens 'a' e 'b' diga qual a parte do circuito que está amostrando o dado de entrada e qual parte do circuito está mantendo o valor anterior.

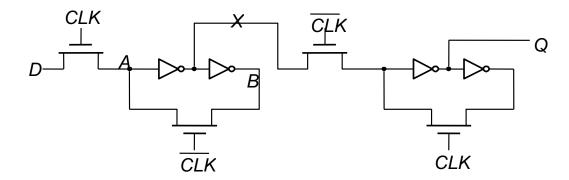

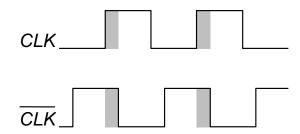

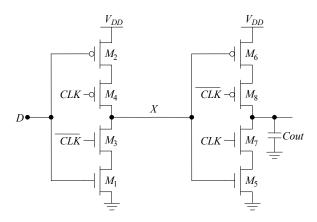

5) Considere o circuito representado abaixo, composto por 4 inversores e 4 transistores N.

- a) Explique seu comportamento, dizendo se o mesmo é sensível à borda (qual borda?) ou ao nível (qual nível?) em relação ao sinal CLK. Jus<u>tifiq</u>ue a resposta ilustrando o comportamento do circuito para cada fase do *clock*, assumindo CLK sem defasem temporal em relação ao sinal de CLK.

- b) Assumir agora que a árvore de relógio gere os sinais de *clock* como abaixo, com sobreposição\_nos níveis lógico '1' e '0'. O que ocorre com este circuito quando há sobreposição dos sinais de clock no nível '1'? Aponte uma possível solução para reduzir os problemas relacionados a este problema (*clock overlapping*).

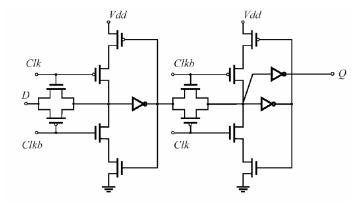

6) Explique o comportamento dos circuitos abaixo. Diga para cada circuito, se o seu comportamento é equivalente a um flip-flpp *latch* ou a um mestre-escravo (**ver lâminas da aula**).

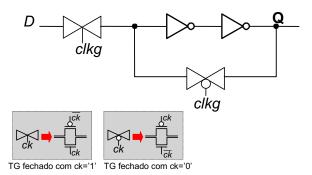

- 7) Considere o circuito representado ao lado.

- a) Explique o comportamento do circuito ao lado, considerado o sinal *clkg* como um pulso. Diga como se comporta o nodo 'Q' em função do pulso *clkg*.

- b) Este circuito opera como um circuito de armazenamento do tipo *latch* ou mestre escravo?

- c) Desenhe a forma de onda esperada para o sinal Q.

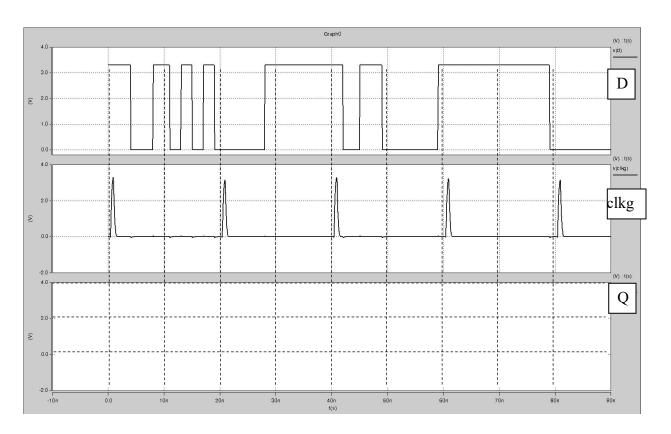

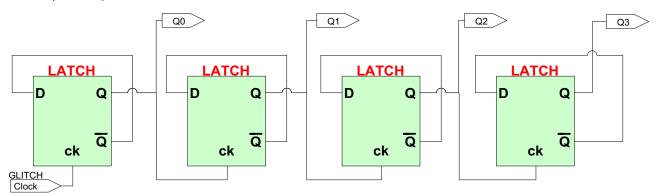

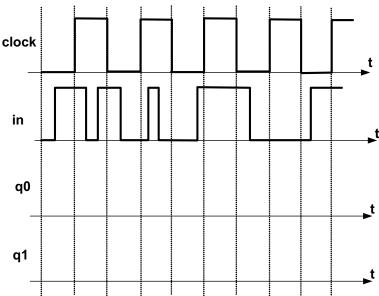

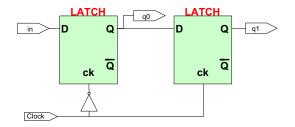

- 8) Utilizando uma latch D, um dado projetista resolveu substituir os FFDs mestre-escravos do contador, utilizando um clock na forma de pulso no primeiro bit. Pede-se:

- a) Explique o comportamento deste novo circuito, dizendo se o mesmo vai operar como um contador ou não.

- b) Apresente as formas de onda para *clock* (*glitch*), e o que se obtém nos sinais Q0 e Q1 [Q2 e Q3 são opcionais].

9) Armazenamento. Considere o circuito representado abaixo:

10) Armazenamento. Considere o circuito representado ao lado. Explique seu comportamento em relação à borda de clock. O circuito armazena o dado na borda de subida, na borda de descida, ou em ambas? Explique através de um diagrama de formas de onda.

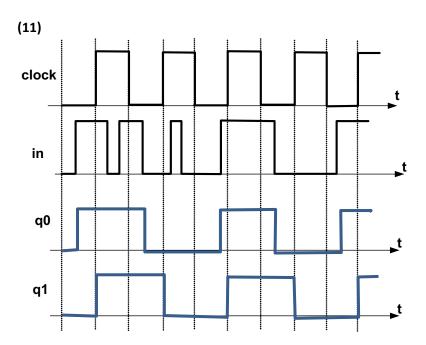

11) A circuito abaixo é composto por duas *latches* transparentes em nível lógico '1' em relação ao sinal *clock*. Dado o diagrama de tempos para os sinais *clock* e *in*, apresente a saída esperada em q0 e q1 (assumir que q0 e q1 iniciam com valor lógico '0', e que não há violação de tempo de *setup* de *in* em relação ao *clock*).

- a) Desenhe o circuito equivalente para os níveis de *CLK=*'0' e *CLK=*'1', explicando o comportamento do circuito.

- b) O circuito, para armazenamento da entrada D, é sensível ao <u>nível</u> ou à <u>borda</u> do sinal clock (CLK)? Se for sensível ao nível do sinal clock, para qual nível o circuito é transparente, ou se for sensível à borda, para qual borda o circuito armazena a informação.

- c) Explique o comportamento do circuito quando <u>acontecer clock overlap</u> em '1' ou seja, *CLK*='1' e *CLK*='1'. Para a explicação desenhe também o circuito equivalente.

# **CIRCUITOS ARITMÉTICOS**

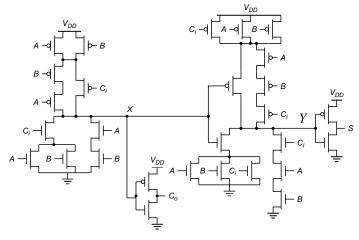

12) Dado o circuito ao lado, composto por 4 portas lógicas (2 portas complexas e dois inversores). Apresente a tabela verdade para os sinais {X, Co, Y e S}, e justifique porque o mesmo implementa um Full-Adder.

- 13) Durante o estudo de operadores aritméticos, foram estudadas cinco arquiteturas de somadores, com as seguintes características:

- a/ duplicação do cálculo de vai-um, e utilização de multiplexadores;

- b/ utilização da propriedade *propagação* para acelerar o cálculo do vai-um;

- c/ arranjo em árvore de somadores simples;

- d/ cálculo explícito da geração de vai-um através de uma porta complexa;

- e/ propagação do vai-um bit-a-bit.

#### Pede-se:

- diga o nome de cada um destes somadores;

- analisando o compromisso área versus desempenho, qual somador você utilizaria para as seguintes configurações: (a) até 12 bits; (b) entre 12 e 32 bits; (c) acima de 32 bits. Justifique as escolhas.

- 14) Dentre os somadores estudados, explique para a arquitetura Carry Look-Ahead:

- a) princípio de funcionamento;

- b) limitações deste somador;

- c) para a equação do gerador de vai-um do quarto bit: mostre como obtê-la, e o diagrama de transistores da função. Dica: use a expansão recursiva da expressão do vai-um do quarto bit: C3 = G3 + P3.C2

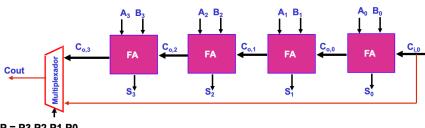

- 15) Apresenta-se abaixo o diagrama do somador carry-bypass para 4 bits. Pede-se:

- a) Qual o princípio de funcionamento deste somador?

- b) Como é construído um somador carry-bypass para 20 bits?

- c) Porque o bypass é mais rápido, mesmo quando todos os módulos do bypass não adiantam o vai-um.

BP = P3.P2.P1.P0

16) Apresenta-se abaixo o diagrama de um módulo do somador *carry-select* para 4 bits. Considerando que desejamos implementar um somador de 64 bits, teremos 16 módulos de 4 bits (N=64, M=4). Considerando apenas o tempo do FA (4 ns) e o tempo do multiplexador (1ns), diga qual o atraso máximo esperado para este somador carry-select de 64 bits, e qual o atraso máximo para o ripple-carry de 64 bits. Qual o número transistores, qual o número total de transistores para cada um dos somadores?

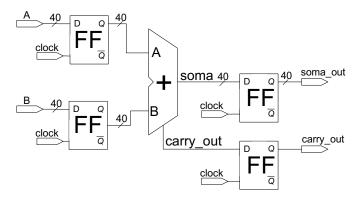

17) Considere o circuito ao lado, composto por 2 entradas de 40 bits (A e B), e 2 saídas (soma\_out de 40 bits, e carry\_out, 1 bit). O tempo de um estágio em um circuito pipeline compreende o atraso devido aos registradores e à lógica combinacional. Os operandos A e B são armazenados no FFs de entrada e somados. Os FFs de saída (segundo estágio) armazenam a soma das entradas do ciclo de clock anterior. O projetista utilizará um somador ripple-carry.

O flip-flop D contém **10** transistores. O somador completo (FA) **28** transistores, tFA = 40 ps. Complete a tabela abaixo (apresentar de forma clara os cálculos na folha de respostas). O cálculo do número total de transistores do circuito deve considerar o somador *ripple-carry* de 40 bits e os flip-flops.

|                                         | FF       |                         | Atraso do       | Atraso do       | Freq. de          | N# de                    |  |

|-----------------------------------------|----------|-------------------------|-----------------|-----------------|-------------------|--------------------------|--|

| Circuito com<br>somador<br>ripple-carry | D→Q (ps) | t <sub>Setup</sub> (ps) | somador<br>(ps) | estágio<br>(ps) | operação<br>(MHz) | transistores do circuito |  |

|                                         | 20       | 5                       |                 |                 |                   |                          |  |

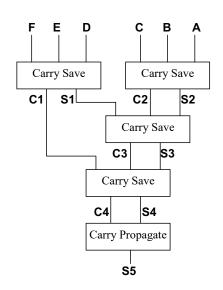

18) O somador *carry save*, utilizado nos multiplicadores, serve para realizar a soma quando há várias parcelas a serem adicionadas.

Dados os seguintes valores:

$A = 001101 (13_{10})$

$B = 000101 (5_{10})$

$C = 001011 (11_{10})$

$D = 001010 (10_{10})$

$E = 000111 (7_{10})$

$F = 001100 (12_{10})$

Mostre a obtenção e os valores de (C1/S1), (C2/S2), (C3/S3), (C4/S4) e a soma final (S5).

| D  | 0 | 0 | 1 | 0 | 1 | 0 |   | Α              | \   | 0 | 0 | 1 | 1 | 0 | 1 |

|----|---|---|---|---|---|---|---|----------------|-----|---|---|---|---|---|---|

| Е  | 0 | 0 | 0 | 1 | 1 | 1 |   | E              | 3   | 0 | 0 | 0 | 1 | 0 | 1 |

| F  | 0 | 0 | 1 | 1 | 0 | 0 |   | C              | ,   | 0 | 0 | 1 | 0 | 1 | 1 |

| S1 |   |   |   |   |   |   |   | S2             | 2   |   |   |   |   |   |   |

| C1 |   |   |   |   |   |   |   | C2             | 2   |   |   |   |   |   |   |

|    |   |   |   |   |   |   |   | S <sub>1</sub> |     |   |   |   |   |   |   |

|    |   |   |   |   |   |   |   | S              | 3 ┌ |   |   |   |   |   |   |

|    |   |   |   |   |   |   |   | C              | 3   |   |   |   |   |   |   |

|    |   |   |   |   |   |   | _ | C              |     |   |   |   |   |   |   |

|    |   |   |   |   |   |   |   | S              | 1   |   |   |   |   |   |   |

|    |   |   |   |   |   |   |   | C4             | Į.  |   |   |   |   |   |   |

|    |   |   |   |   |   |   |   | Soma           | 3   |   |   |   |   |   |   |

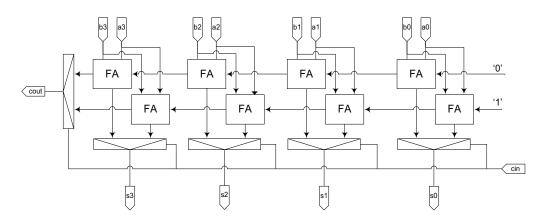

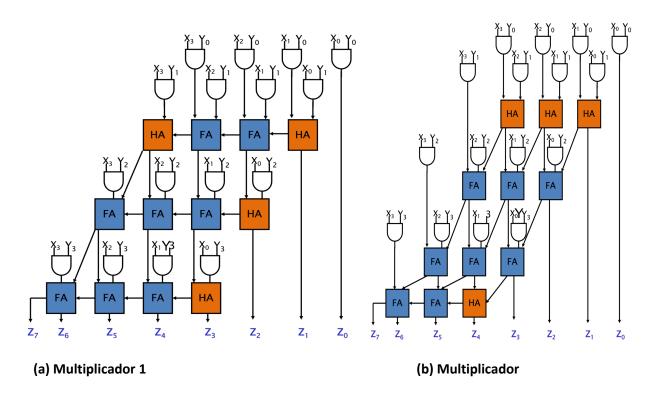

- 19) Multiplicação. Apresenta-se abaixo o diagrama lógico de dois multiplicadores de 4x4 bits.

- (a) Qual a diferença entre os dois multiplicadores, e indique qual é o mais rápido. Justifique a resposta.

- (b) Considerando que o FA (somador completo) tem 28 transistores e o HA (meio somador) 14 transistores, qual o número total de transistores para o somador mais rápido?

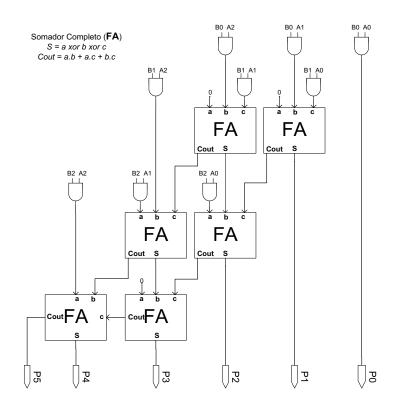

20) Apresenta-se abaixo o diagrama lógico de um multiplicador de 3 bits.

Dados os seguintes valores:

$$A = 101 (5_{10})$$

$B = 011 (3_{10})$

- a) Mostrar no desenho todos os valores de entrada e saída dos FA, assim como o valor do produto final.

- b) Calcular e apresentar o número de transistores dês multiplicador.

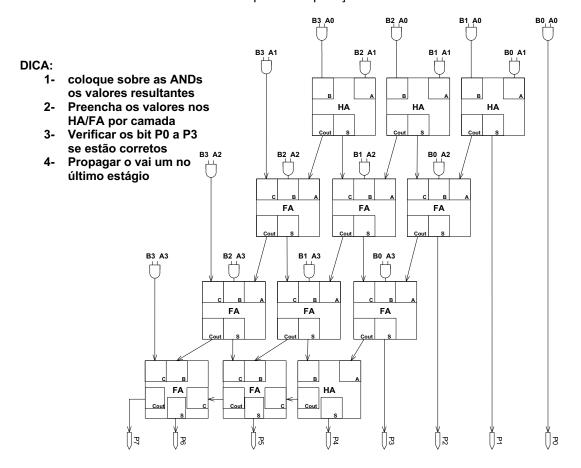

- 21) Multiplicação. Apresenta-se abaixo o diagrama lógico de um multiplicador de 4 bits.

- d) explique como o carry é propagado no interior do circuito.

- e) Considere: A=1101 e B=1011. Desenhe sobre o circuito os valores booleanos correspondentes, verificando se o valor obtido pela multiplicação é o correto.

22) Operações muito comuns em processadores são os deslocamentos e as rotações. Apresentar uma matriz de transistores capaz de realizar rotações para a direita para palavras de 4 bits. Exemplo de operação:

|       | Entrada                    | А3 | A2 | A1 | A0 |

|-------|----------------------------|----|----|----|----|

| 6.41. | Rot. 1 bit direita         | Α0 | A3 | A2 | A1 |

|       | Rot. 2 bits direita        | A1 | Α0 | А3 | A2 |

| Saída | Rot. 3 bits direita        | A2 | A1 | Α0 | A3 |

|       | Rot. 4 bits direita (null) | А3 | A2 | A1 | Α0 |

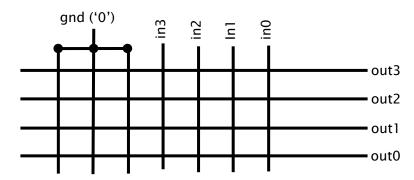

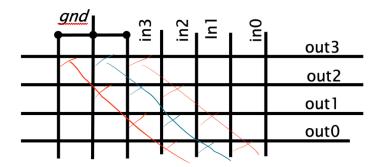

23) Apresentar uma matriz de transistores capaz de realizar deslocamentos para a direita para palavras de 4 bits, onde o bit mais significativo recebe '0' (gnd). A tabela abaixo ilustra os valores que os bits de saída devem receber em função da entrada:

| Ação                           | Comando | out3 | out2 | out1 | out0 |

|--------------------------------|---------|------|------|------|------|

| Não desloca                    | SR0     | in3  | in2  | in1  | in0  |

| Deslocamento de 1 bit direita  | SR1     | 0    | in3  | in2  | in1  |

| Deslocamento de 2 bits direita | SR2     | 0    | 0    | in3  | in2  |

| Deslocamento de 3 bits direita | SR3     | 0    | 0    | 0    | in3  |

Utilize a matriz abaixo para posicionar os transistores que habilitarão a execução dos comandos {SR0, SR1, SR2, SR3}.

Para os comandos {SR1, SR2, SR3}, que modificação simples este circuito poderia receber para inserir nos bits que hoje recebem '0' (em cinza na tabela) a possibilidade de selecionar 1 dentre 3 valores {'0', '1', in3} em função de um sinal de controle denominado **select**? A possibilidade de selecionar *in3* permite realizar deslocamentos aritméticos. Mostrar esta modificação no desenho.

## **FLUXO DE PROJETO**

- 24) Descreva o nível de precisão que o projetista obtém como informação do funcionamento do circuito com:

- a) simulação VHDL;

- b) simulação com VHDL ou Verilog mapeado após a síntese, com anotação de atraso SDF;

- c) simulação Spice após extração lógica obtida do layout.

- 25) O projeto de circuitos integrados pode ser feito segundo diferentes métodos, como full custom, standard-cells, gate array, FPGA, entre outros. As figuras abaixo caracterizam dois dos métodos acima relacionados. Preencha a tabela conforme os itens solicitados.

|                                                                                              | PMOS NMOS NMOS |

|----------------------------------------------------------------------------------------------|----------------|

| Nome do método de projeto                                                                    |                |

| <b>Camadas</b> que devem ser fabricadas na <i>foundry</i>                                    |                |

| <b>Reuso</b> de <i>wafers</i> com circuitos préfabricados(possível ou impossível, e a razão) |                |

| Custo<br>(maior ou menor, e a razão)                                                         |                |

26) O projeto de circuitos eletrônicos pode ser feito utilizando diferentes métodos de projeto. Avalie estes métodos de projetos quantos aos requisitos abaixo:

| ESTILO DE PROJETO:                                                    | FPGA | Gate  | Standard | Full   |

|-----------------------------------------------------------------------|------|-------|----------|--------|

| ESTILO DE PROJETO:                                                    | FPGA | array | cell     | custom |

| Quais as camadas que devem ser fabricadas na foundry?                 |      |       |          |        |

| Respostas: T: todas / algumas (dizer quais) / N: nenhuma              |      |       |          |        |

| Tamanho da célula.                                                    |      |       |          |        |

| Respostas: F: fixo / L: livre / H: variável, mas com altura constante |      |       |          |        |

| Interconexão entre as células.                                        |      |       |          |        |

| Respostas: M: apenas metalização / Q: qualquer camada /               |      |       |          |        |

| C: configurável                                                       |      |       |          |        |

27) *Métodos de projeto* In semiconductor design, standard cell methodology is a method of designing Application Specific Integrated Circuits (ASICs). Standard cell methodology is an example of design abstraction, whereby a low-level VLSI-layout is encapsulated into an abstract logic representation (such as a NAND gate). Cell-based methodology makes it possible for one designer to focus on the high-level (logical function) aspect of digital-design, while another designer focused on the implementation (physical) aspect. Along with semiconductor manufacturing advances, standard cell methodology was responsible for allowing designers to scale ASICs from comparatively simple single-function ICs (of several thousand gates), to complex multi-million gate devices (SoC).

<u>Descreva</u> as principais etapas de projeto do método *standard cell* na forma de itens, do VHDL ao layout. Para cada etapa elabore ao menos uma frase (não escreva um simplesmente por exemplo "simulação funcional").

| Etapa | Descrição |

|-------|-----------|

| ••••• |           |

| ••••• |           |

.....

### **POUCAS SOLUÇÕES:**

**(4)** {X,Y,Z} para clock =1: {not D, pré-carga em 0, alta impedância}, ou seja, amostrando a entrada em X e mandando o valor em Q

{X,Y,Z} para clock =0: {ultimo valor amostrado, Y fica sem 0 se último valor de D era '0' senão carrega Y, Z é Y negado e Q Z negado}, ou seja transfere a entrada D para a saída na BORDA de descida.

Quando ao D: no nível alto do clock ele está sendo amostrado - sem problemas

no nível baixo do clock um D=0 pode colocar X em '1', o que não é problema pois X está conectado a um transistor P. Logo, variação de D com clock='0' não é problema.

a/ com com um glitch a latch opera como mestre escravo e reduz o número de transistores

b/ não vai operar como um contador, o primeiro bit opera corretamente, como um divisor de clock, mas o segundo bit oscila, ficando em modo transparente quant Q0 for 1

(17)

|              |    |   | Atraso somador 40 bits | Atraso (ps) | Freq.<br>(MHz) | N# total de<br>transistores |

|--------------|----|---|------------------------|-------------|----------------|-----------------------------|

| ripple-carry | 20 | 5 | 40* 40ps = 1600 ps     | 1625 ps     | 615,38         | 1120+1210=<br>2330          |

Flops: 121 \* 10 = 1210 Ripple: 28 \* 40 = 1120

(23) Linhas de controle com inclinação de -45 graus

Para a parte final é só colocar um mux.

### (26) Estilos de projeto

| ESTILO DE PROJETO:                                                    | FPGA | Gate    | Standard | Full   |

|-----------------------------------------------------------------------|------|---------|----------|--------|

| ESTILO DE PROJETO.                                                    | FPGA | array   | cell     | custom |

| Quais as camadas que devem ser fabricadas na foundry?                 |      | Metal/  |          |        |

| Respostas: T: todas / algumas (dizer quais) / N: nenhuma              | N    | contato | T        | Т      |

| Tamanho da célula.                                                    |      |         |          |        |

| Respostas: F: fixo / L: livre / H: variável, mas com altura constante | F    | F       | H        | L      |

| Interconexão entre as células.                                        |      |         |          |        |

| Respostas: M: apenas metalização / Q: qualquer camada /               |      |         |          |        |

| C: configurável                                                       | P    | M       | Q        | Q      |