# MICROELETRÔNICA LISTA DE EXERCÍCIOS – UNIDADE 1

Fernando Gehm Moraes 15/setembro/2024

1) Explicar na tabela abaixo a influência dos principais parâmetros do transistor MOS na corrente I<sub>ds</sub> (corrente dreno-source).

| Parâmetro       | Ação para <u>aumentar</u> o I <sub>ds</sub> (duas respostas possíveis: aumentar ou diminuir) | Explicar a razão |

|-----------------|----------------------------------------------------------------------------------------------|------------------|

| W               |                                                                                              |                  |

| L               |                                                                                              |                  |

| Mobilidade      |                                                                                              |                  |

| Espessura óxido |                                                                                              |                  |

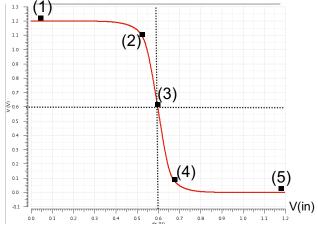

2) A figura abaixo ilustra a curva DC do inversor, para o caso que o dimensionamento Wp/Wn é equivalente ao fator de mobilidade  $\mu n/\mu p$  (Wp/Wn =  $\mu n/\mu p$ ).

V(out)

| Ponto | NMOS | PMOS |

|-------|------|------|

| 1     |      |      |

| 2     |      |      |

| 3     |      |      |

| 4     |      |      |

| 5     |      |      |

#### Pede-se:

- a) Qual o estado dos transistores N e P para cada um dos 5 pontos da curva, completando a tabela acima com as letras: C, L, S(cortado, linear (ou resistivo), saturado).

- b) Como ficaria esta curva DC no caso do dimensionamento Wp/Wn <μn/μp? Justifique, desenhando a nova curva no mesmo gráfico acima.

- 3) Explique por que em células CMOS estáticas deve haver dualidade nas conexões (série em uma plano e paralelo no outro plano). Mostrar através de exemplos os problemas que podem ocorrer.

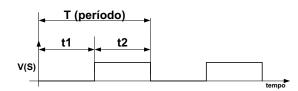

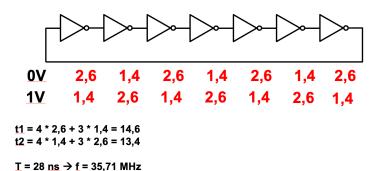

- 4) Oscilador em anel. Considere um oscilador em anel de 7 estágios, tendo o inversor tr=2,6 / e tf=1,4 ns. Determine t1, t2, período e frequência.

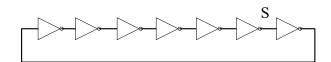

5) A figura abaixo ilustra um oscilador em anel.

#### Pede-se:

- (a) Dado que tr=1.0 ns (tempo de propagação de subida de um inversor) e tf=0.5 ns (tempo de propagação de descida de um inversor), qual o período (unidade: ns) e a frequência (unidade: MHz) resultante no nodo S?

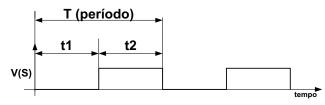

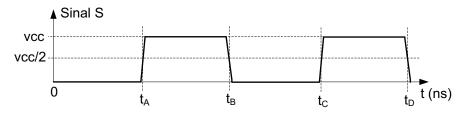

- (b) A figura abaixo ilustra a saída do oscilador. Determine os tempos tA, tB, tC, tD, mostrando como eles foram obtidos. Como os tempos de subida e descida são diferentes, o dutty cycle não é 50%.

6) Considere um oscilador em anel de 5 estágios, tendo o inversor **tr=3,5 ns** (tempo de propagação de subida de um inversor) e **tf=4,5ns** (tempo de propagação de descida de um inversor).

#### Pede-se:

- a) Determine os tempos t1 e t2 (em ns) explique o procedimento para obter os valores?

- S

b) Em função de t1 e t2, determine T e diga qual a frequência de oscilação (em MHz).

#### 7) Portas NAND/NOR

- a. Considerar uma porta NAND com tamanho de transistores constantes. Trace em um mesmo gráfico os tempos de subida e descida em função do número de entradas (no eixo y o atraso da porta e no eixo x número de entradas da porta), supondo a variação de apenas uma entrada. Explique o comportamento apresentado.

- b. Repita o item anterior para a porta NOR, também com tamanho de transistores constantes.

- c. Explique o impacto da posição da entrada da porta lógica no atraso da mesma.

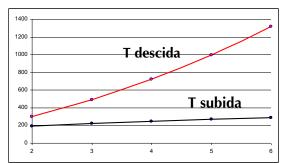

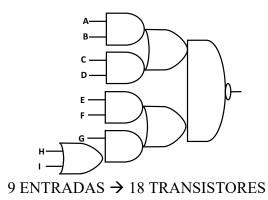

- 8) O gráfico abaixo apresenta no **eixo y** o **atraso** da porta lógica, e no **eixo x** o **número de entradas** variando de 2 a 6.

- a) A qual porta lógica corresponde o gráfico?

Fazer um diagrama de transistores para 4 entradas.

- b) Explique o porquê do aumento do tempo de propagação de descida, e o motivo do tempo de subida ser praticante constante.

## PORTAS LÓGICAS COMPLEXAS

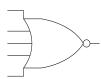

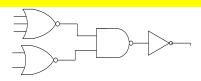

9) Devido à limitação do número de transistores em série, portas lógicas com mais de 4 transistores não são utilizadas, devido ao aumento da tensão de *threshold*. Considere a porta lógica abaixo, uma *nor* de 5 entradas.

Utilizando os teoremas de De Morgan, descritos abaixo, desenhe um circuito lógico equivalente, utilizando portas *nands, nors* e inversor, com no máximo 3 entradas.

$$not (P \ and \ Q) = (not \ P) \ or \ (not \ Q)$$

$not (P \ or \ Q) = (not \ P) \ and \ (not \ Q)$

- 10) Implemente a seguinte função: Y = (A+B)C + BD + ACD + AC + BCD + AD com no máximo 10 transistores. Logicamente, deve-se minimizar esta equação, e depois implementá-la via portas complexas. Faça os diagramas lógicos e elétrico da função minimizada. Dica: determine a função Y minimizada (será a porta complexa) e acrescente um inversor na saída.

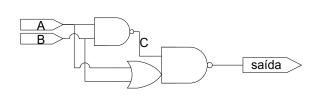

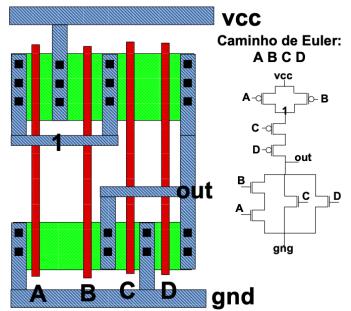

- 11) Considere a circuito abaixo, composto de uma porta lógica nand e uma porta complexa:

Pede-se:

- a) Diagrama de transistores

- b) Número de transistores

- c) Função lógica da porta (faça a tabela verdade e diga à qual função corresponde)

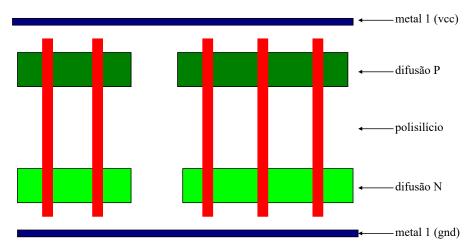

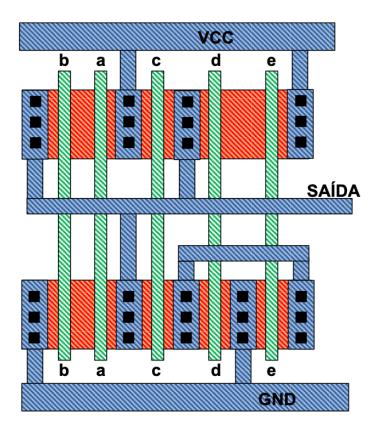

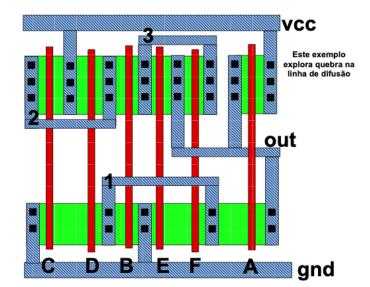

- d) Diagrama de *stick* do circuito. Para o diagrama *stick* utilize o layout abaixo para ponto de partida. Não há necessidade de quebras nas linhas de difusão para este exemplo.

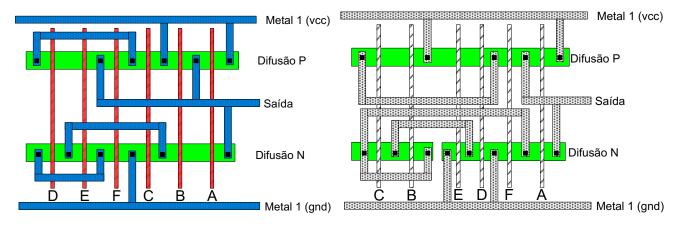

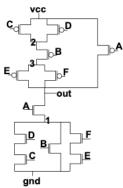

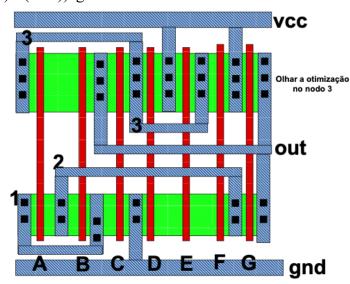

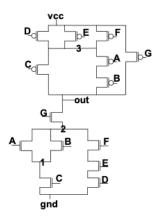

12) Considere os diagramas stick abaixo:

#### Para cada um deles determinar:

- a. Número de transistores total, número de transistores N, número de transistores P

- b. Diagrama de transistores

- c. Diagrama lógico

- d. Qual o número máximo de transistores há em série no plano N (conjunto de transistores N) e no plano P?

- e. Se esta mesma função fosse implementada com portas simples (*nand, nor, inversor*) quantos transistores seriam necessários? Justifique.

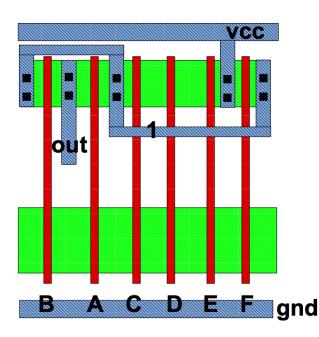

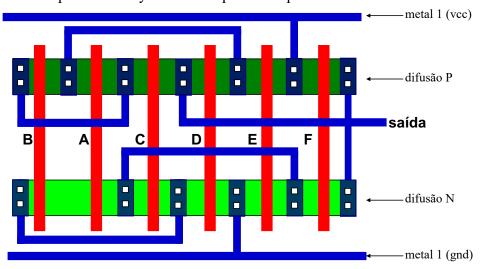

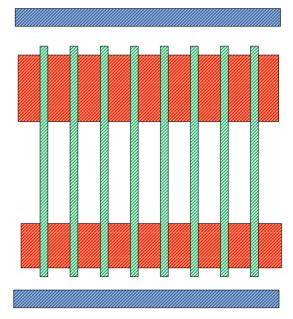

- 13) Considere o layout abaixo, com apenas os transistores P roteados.

- a) Determine o diagrama de transistores P do layout ao lado, e usando o princípio da dualidade de conexões série/paralelo determine o diagrama de transistores N.

- b) Complete o layout para o plano N.

- c) Qual é a função lógica desta porta complexa (na forma de uma equação lógica)?

- d) Número total de transistores, número máximo de transistores em série no plano N e número máximo de transistores em série no plano P.

- e) Quantos transistores seriam necessários para implementar esta porta lógica complexa, utilizando apenas portas lógicas NAND-NOR-INV. Justifique a resposta apresentando o diagrama lógica de ambas implementações (porta complexa e portas simples).

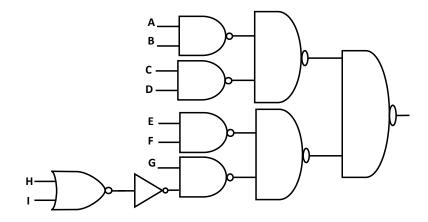

- 14) Considere a seguinte equação lógica:  $F = \overline{((a.b + c.d).(e.f + g.(h + i)))}$ . Pede-se:

- a. Diagrama lógico

- b. Diagrama de transistores

- c. Número de transistores

- d. Quantos transistores há em série no plano N (conjunto de transistores N) e no plano P?

- e. Se esta mesma função fosse implementada com portas simples (nand, nor, inversor) quantos transistores seriam necessários? Qual seria a profundidade lógica desta implementação sem portas complexas? Desenhe o circuito lógico equivalente.

- 15) A figura abaixo representa o layout de uma porta complexa.

#### Pede-se:

- a) Identifique no layout acima em um transistor qualquer os parâmetros W e o L.

- b) Desenhe o diagrama de transistores (N e P) desta porta lógica

- c) Qual é a função lógica desta porta? (no formato  $F = \overline{((a.b + c.d).(e.f + g.(h + i)))}$ )

- 16) Considere o netlist spice abaixo, o qual representa uma porta lógica CMOS complexa, dual:

| MN1     | out | e1 | 3    | gnd  | NMOS L=0.8U W=8U AD=17.6P AS=17.6P PD=20.4U PS=20.4U |

|---------|-----|----|------|------|------------------------------------------------------|

| MN2     | out | e2 | 3    | gnd  | NMOS L=0.8U W=8U AD=17.6P AS=17.6P PD=20.4U PS=20.4U |

| MN3     | out | e3 | 3    | gnd  | NMOS L=0.8U W=8U AD=17.6P AS=17.6P PD=20.4U PS=20.4U |

| MN4     | 3   | e4 | 4    | gnd  | NMOS L=0.8U W=8U AD=17.6P AS=17.6P PD=20.4U PS=20.4U |

| MN5     | 3   | e5 | 4    | gnd  | NMOS L=0.8U W=8U AD=17.6P AS=17.6P PD=20.4U PS=20.4U |

| MN6     | 3   | e6 | 4    | gnd  | NMOS L=0.8U W=8U AD=17.6P AS=17.6P PD=20.4U PS=20.4U |

| MN7     | 4   | e7 | gnd  | gnd  | NMOS L=0.8U W=8U AD=17.6P AS=17.6P PD=20.4U PS=20.4U |

| MN8     | out | e8 | gnd  | gnd  | NMOS L=0.8U W=8U AD=17.6P AS=17.6P PD=20.4U PS=20.4U |

| MP9     | out | e1 | 5    | vcc  | PMOS L=0.8U W=8U AD=17.6P AS=17.6P PD=20.4U PS=20.4U |

| MP10    | 5   | e2 | 6    | vcc  | PMOS L=0.8U W=8U AD=17.6P AS=17.6P PD=20.4U PS=20.4U |

| MP11    | 6   | e3 | 9    | vcc  | PMOS L=0.8U W=8U AD=17.6P AS=17.6P PD=20.4U PS=20.4U |

| MP12    | out | e4 | 7    | vcc  | PMOS L=0.8U W=8U AD=17.6P AS=17.6P PD=20.4U PS=20.4U |

| MP13    | 7   | e5 | 8    | vcc  | PMOS L=0.8U W=8U AD=17.6P AS=17.6P PD=20.4U PS=20.4U |

| MP14    | 8   | e6 | 9    | vcc  | PMOS L=0.8U W=8U AD=17.6P AS=17.6P PD=20.4U PS=20.4U |

| MP15    | out | e7 | 9    | vcc  | PMOS L=0.8U W=8U AD=17.6P AS=17.6P PD=20.4U PS=20.4U |

| MP16    | 9   | e8 | vcc  | vcc  | PMOS L=0.8U W=8U AD=17.6P AS=17.6P PD=20.4U PS=20.4U |

| 1411 10 | ,   | -0 | , 50 | , 50 | 111105 L 0.00 1, 00 1D 17.01 1D 20.40 15 20.40       |

#### **Pede-se:**

- a) Diagrama de transistores (compreensível)

- b) Diagrama lógico

- c) Número de transistores total, número máximo de transistores em série no plano N, e número máximo de transistores em série no plano P.

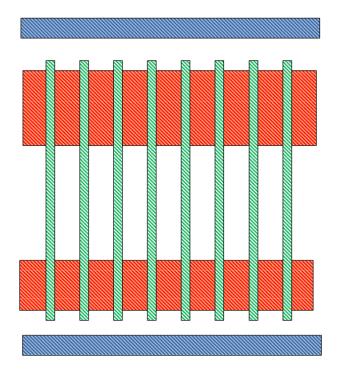

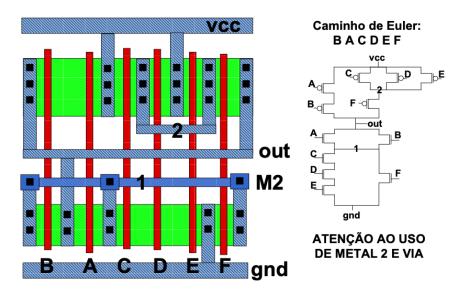

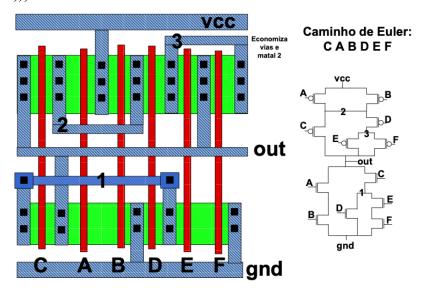

- d) Complete o *layout* desta porta lógica, sobre o modelo apresentado na figura abaixo (esta célula tem garantidamente caminho dual em ambos os planos), diferenciando os níveis de metal. **Não** alterar a ordem dos transistores.

- e) Se esta mesma função fosse implementada com portas simples (*nand, nor, inversor*) quantos transistores seriam necessários? Justifique.

#### 17) Considere o layout abaixo:

- a. Determine o diagrama de transistores desta porta lógica (fazer desenho compreensível)

- b. Para o vetor de entrada ABCDE = {11011} determine o valor lógico da saída.

- c. Esta porta lógica está corretamente projetada? Tanto em caso afirmativo como negativo, justificar a resposta

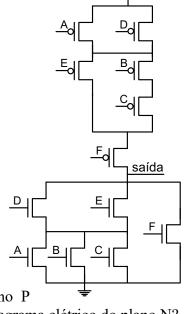

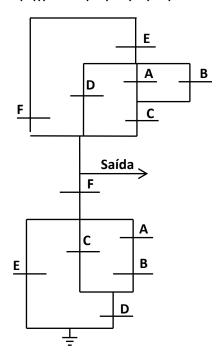

- 18) Considere a porta complexa ao lado.

- a. Qual o valor observado na saída quando A='1', B='0', C='0', D='0', E='1', F='0'? Esta porta está corretamente projetada? Em caso negativo, explique o motivo.

- b. Caso esta porta esteja mal projetada, considere que o plano P represente a função desejada pelo projetista. Como ficaria o diagrama elétrico do plano N?

- 19) Considere as equações lógicas abaixo:

## Pede-se para cada função ao lado:

- a) Diagrama lógico.

- b) Diagrama de transistores.

- c) Layout (stick) de cada função.

- d) Número de transistores total, número de transistores no plano N/P, número de transistores em série em cada plano.

$$F_{1} = \overline{(a.b + c + d)}$$

$$de \quad F_{2} = \overline{(a + b) \cdot (c.d.e + .f)}$$

$$F_{3} = \overline{(a.b) + (c.(d + (e.f)))}$$

$$F_{4} = \overline{a.(b + (c.d) + (e.f))}$$

$$F_{5} = (\overline{((a + b) \cdot c.) + (d.e.f)) \cdot g}$$

Utilizar o template abaixo para o diagrama stick:

Solução de F1:  $F_1 = \overline{(a.b+c+d)}$

20) Outras funções de portas complexas que podem ser utilizadas como exercícios:

| Função                            |

|-----------------------------------|

| F = not ((a+b)*(c*d*e+f*g*(h+i))) |

| F = not ((a+b)*(c+d+e*(f*g+h*i))) |

| F = not ((a+b*c*(d+e))*(f+g+h+i)) |

| F = not ((a*b+c*d)*(e*f+g*(h+i))) |

| F = not ((a*(b+c)+d*e*f)*(g+h+i)) |

| F = not ((a+b+c*d)*(e+f+g*(h+i))) |

| F = not ((a+b+c*(d+e))*(f+g+h+i)) |

| F = not ((a+b+c+d)*(e+f+g+h*i))   |

| F = not (a*b*(c+(d+e+f)*(g+h+i))) |

| F = not (a*b*(c+d*e+f*g+h*i))     |

## **DIMENSIONAMENTO DE PORTAS LÓGICAS**

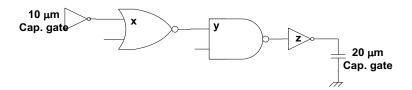

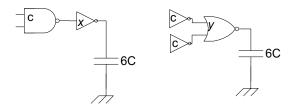

- 21) Considere a rede multi-estágio abaixo. Ao invés de definirmos as capacitâncias por "C", define-se pela capacitância equivalente em x microns de gate. Pede-se:

- a) Atraso mínimo no caminho (em unidades adimensionais de atraso)

- b) Dimensionamento para atraso mínimo do inversor, nand e nor

- c) Contribuição do atraso em cada porta, e verifique se o somatório dos atrasos confere com o atraso mínimo no caminho.

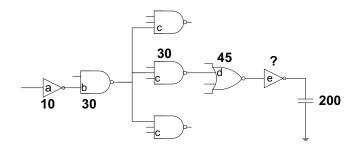

22) Dimensione o seguinte circuito (valores de a, b, e c) para obter o menor tempo de propagação da entrada para saída.

- 23) Considere que o caminho mais longo em um dado circuito compreenda 8 portas lógicas. O caminho crítico compreende 8 portas nand-4, todas com fan-out 3. Determine o atraso d (adimensional) desta seqüência de portas. Atenção: o fator de branch compreende o produtório de 7 saídas e a relação de carga será igual a 3.

- 24) Considere 2 formas distintas de se implementar uma porta AND-2, com uma relação de carga de 6 entre a entrada e a saída. Determine o "esforço do caminho" para ambas as configurações. Qual das duas configurações é mais rápida? Calcule o tamanho relativo *x* e *y* das portas lógicas para que se obtenha o atraso mínimo.

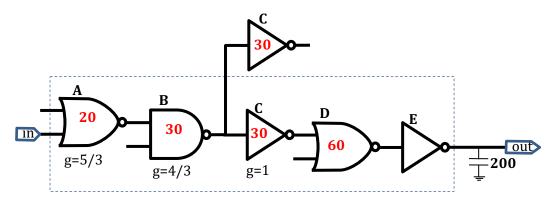

25) Considere o caminho lógico abaixo, entre a porta A com entrada igual a **20** unidades de W, e saída conectada a uma carga equivalente a **200** unidades de W. As portas lógicas {A,B,C,D} já estão dimensionadas, com tamanho de {**20**, **30**, **30**, **60**}.

#### **Pede-se:**

- a) Determine o atraso mínimo do caminho.

- b) Qual o dimensionamento de cada porta lógica considerando o atraso mínimo?

- c) Determine o dimensionamento do inversor E para que o atraso seja igual a 22 unidades de atraso.

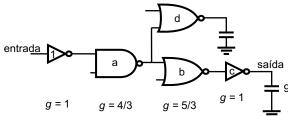

- Considere a rede multi-estágio abaixo, onde as capacitâncias estão definidas por x microns de gates (g\_inv=1, g\_nand2=4/3, g\_nand3=5/3, g\_nor4=9/3).

Neste exercício específico, todas as portas lógicas estão dimensionadas, exceto o inversor de saída. Supondo que o projetista determinou que o atraso neste caminho devesse ser **28** unidades de atraso de propagação, determine o dimensionamento do inversor e. (lembrando: a fórmula de báscara é  $(-b + - sqrt(b^2-4ac))/2a$ .

Dica: não usar a equação de atraso mínimo f. Montar equações de atraso para cada gate utilizando a equação d=g\*h+p. Assim teremos  $d_A+d_B+d_C+d_D+d_E=28$ , resultando em uma equação de segundo grau.

#### Havendo duas soluções possíveis, qual seria a adotada? Por quê?

|   | Dimensionamento (microns) | Atraso da porta           |

|---|---------------------------|---------------------------|

| Α | 10                        | <determinar></determinar> |

| В | 30                        | <determinar></determinar> |

| С | 30                        | <determinar></determinar> |

| D | 45                        | <determinar></determinar> |

| E | <determinar></determinar> | <determinar></determinar> |

|   | Atraso total:             | 28                        |

Qual seria o atraso mínimo no caminho, considerando apenas a relação de carga (H), derivação (B), esforço lógico (G), parasitas e número de estágios?

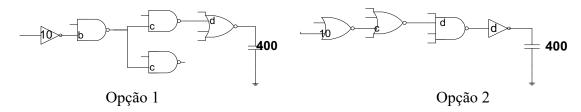

27) O projetista, ao utilizar uma ferramenta de síntese, obteve duas soluções distintas para um mesmo circuito, conforme abaixo. Determine a solução que teria menor área (somatório do dimensionamento dos transistores – 10/b/c/d), e o menor atraso. Justifique as escolhas.

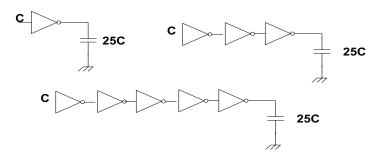

28) Considere que um projetista necessita de uma função inversor para carregar uma carga 25 vezes superior à carga de entrada. O projetista considera 3 opções: um único inversor, três inversores em série e cinco inversores em série.

9

- a) Para a escolha, calcule a contribuição de cada estágio. O que significa este valor no dimensionamento do transistor?

- b) Calcule o atraso mínimo do caminho. Através deste cálculo, diga qual a melhor escolha para o projetista.

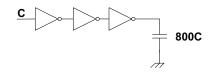

29) Considere que um projetista necessita de uma função inversor para carregar uma carga 800 vezes superior à carga de entrada (isto ocorre, por exemplo, em circuitos de entrada e saída). O projetista considera 4 opções: um único inversor, três inversores em série, cinco inversores em série e sete inversores em série. A figura ao lado ilustra a configuração para 3 inversores em série. Pede-se

- a) Calcule o atraso mínimo do para as 4 configurações (1-3-5-7). Através deste cálculo, diga qual a melhor escolha para o projetista.

- b) Para a configuração escolhida, determine o dimensionamento de cada inversor.

#### Fórmulas úteis:

- atraso mínimo em um caminho:  $\hat{D} = N.F^{\frac{1}{N}} + P$ , onde N corresponde ao número de estágios e F o esforco docaminho.

- $\mathbf{F} = \mathbf{G.B.H}$ , onde:

- G é o esforço lógico do caminho:  $G = \prod g_i$

- B é a influência da derivações no caminho:  $B = \prod b_i$ , onde  $b_i = \frac{C_{total}}{C_{useful}}$

- H é a relação entre a capacitância de saída pela capacitância de entrada

- a contribuição de cada estágio ao longo de um caminho para se obter o atraso mínimo é dado por:

$$\hat{f} = g_i.h_i = F^{\frac{1}{N}}$$

- de posse da contribuição de cada estágio, dimensiona-se a porta lógica:  $C_{in} = \frac{g_i \cdot C_{out}}{f}$

- atraso de uma porta: d = g.h + p (onde g é o esforço lógico)

| g (esforço Lógico) | 1 | 2   | 3   | 4   | 5    | n        |

|--------------------|---|-----|-----|-----|------|----------|

| Inversor           | 1 |     |     |     |      |          |

| Nand               |   | 4/3 | 5/3 | 6/3 | 7/3  | (n+2)/3  |

| Nor                |   | 5/3 | 7/3 | 9/3 | 11/3 | (2n+1)/3 |

## **INTEGRANDO OS TÓPICOS**

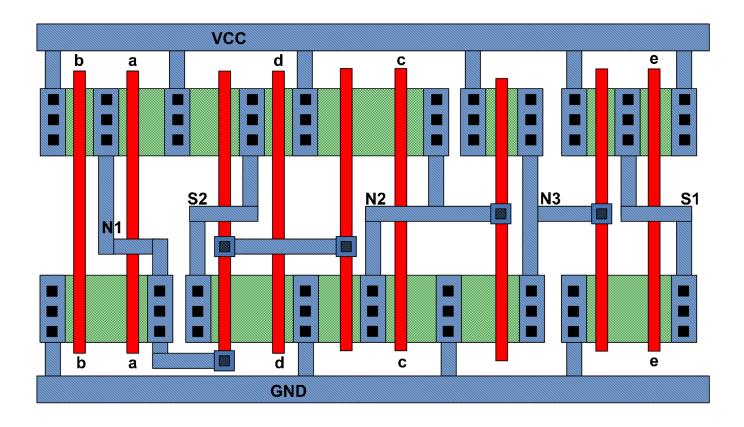

- 30) Considere o layout abaixo, composto por portas lógicas NAND, NOR e INVERSOR, entradas {a,b,c,d,e}, nodos internos {N1,N2,N3} e saídas {S1,S2}. Neste layout não há utilização de METAL2, nem VIAS.

- a. Faça o diagrama de portas lógicas do layout. Para cada porta lógica, indicar as entradas e saídas com o labels do layout ( {a,b,c,d,e,N1,N2,N3,S1,S2} ).

- b. A partir do diagrama lógico obtido, indicar qual a parte deste circuito que pode ser **otimizada** com uma **porta complexa**.

- b.1) Determine o diagrama de transistores desta porta lógica complexa e o correspondente diagrama lógico..

- b.2) Apresente o diagrama *stick* desta porta lógica, indicando as camadas utilizadas.

- b.3) Qual o número total de transistores do circuito com e sem a otimização proposta?

- c. Considerar que o dimensionamento da porta lógica com entradas {a,b} no layout apresentado seja de 2 (2 unidades de dimensionamento) e que a carga de saída seja 5 vezes superior a este dimensionamento.

- c.1) Determine o atraso mínimo do caminho mais longo (saídas de portas lógicas com labels N1, N2, N3, S1). Considerar na derivação portas de mesmo dimensionamento. (g inv=1, g nand2=4/3, g nand3=5/3, g nor2=5/3, g nor3=7/3).

- c.2) Determine o dimensionamento das portas lógicas neste caminho.

- c.3) Determine o atraso de cada porta lógica.

## LÓGICA DINÂMICA

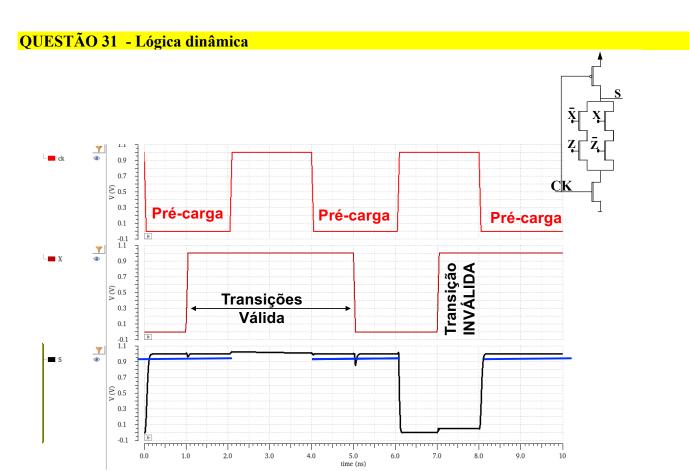

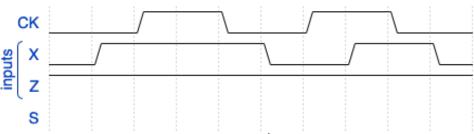

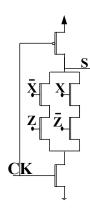

31) Explique a operação de portas com lógica dinâmica utilizando o exemplo ao lado.

Para o diagrama de tempos apresentados, indicar o valor esperado em 'S', indicando se as transições em 'X' são válidas ou não ('Z' está em '1')

32) Explique o que é lógica dinâmica DOMINÓ, e onde a mesma é utilizada.

# **ALGUMAS SOLUÇÕES**

**OUESTÃO 4 – Oscilador em anel**

#### QUESTÃO 5 – Oscilador em anel

t subida - 1 ns t descia = 0.5 ns

PARA SUBIR

$$1 + 0.5 + 1 + 0.5 + 1 + 0.5 + 1 = 5.5 \text{ NS}$$

PARA DESCER

$$0.5 + 1 + 0.5 + 1 + 0.5 + 1 + 0.5 = 5 \text{ NS}$$

$$TA = 5.5$$

$TB = 10.5$   $TC = 16$  NS etc

#### **QUESTÃO 9 – NOR de 5 entrads**

#### QUESTÃO 10 – Minimização e porta complexa

$$F = AC + BC + BD + ACD + AC + BCD + AD = AC + BC + BD + AD = (A+B).(C+D)$$

A porta lógica terá 8 transistores + 2 inversores → total 10 transistores.

#### **QUESTÃO 11**

Porta lógica XNOR, com 10 transistores

Solução: lâminas microel slides 03 – Lâmina 21 – exercício 1/8

#### **QUESTÃO 12**

Solução A: lâminas microel slides 03 – Lâmina 22 – exercício 2/8

Solução B: lâminas microel slides 03 – Lâmina 25 – exercício 3/8

#### **QUESTÃO 13**

Solução A: lâminas microel slides 03 – Lâmina 34– exercício 8/8

## QUESTÃO 14 – porta complexa - $F = \overline{((a.b + c.d) \cdot (e.f + g.(h + i)))}$

Sem portas complexas 34 (8\*4 2) transistores, com profundidade lógica igual a 5

(usando De Morgan: soma de produtos implementa com NANDS)

### **QUESTÃO 15 - Porta complexa**

Solução da porta complexa F = not ( (((AB+C).D)+E).F) )

#### **QUESTÃO 16 - Porta complexa**

Solução B: lâminas microel slides 03 – Lâmina 30– exercício 6/8

#### **QUESTÃO 17 - Porta complexa**

Solução B: lâminas microel slides 03 – Lâmina 28– exercício 5/8

#### **QUESTÃO 19 - Porta complexas**

$$F_2 = \overline{(a+b).(c.d.e+.f)}$$

$$F_3 = \overline{(a.b) + (c.(d+(e.f)))}$$

$$F_4 = \overline{a \cdot (b + (c \cdot d) + (e \cdot f))}$$

#### Caminho de Euler (só no plano N): C D B E F A

$$F_5 = (\overline{((a+b).c.) + (d.e.f)).g}$$

#### Caminho de Euler: ABCDEFG

#### QUESTÃO 21 – rede multi-estágio inv nor nand inv

- $G = 1 \cdot (5/3) \cdot (4/3) \cdot 1 = 20/9 = 2,22$

- B = 1

- H = 20/10 = 2

- F = GBH = 40/9 = 4.44

(a)

$$\mathbf{D} = \text{N.F exp} (1/\text{N}) + P = 4 \cdot (40/9) \exp(1/4) + 6 = 11.8$$

- (b)  $f = (40/9) \exp(1/N) = 1,452$

- -z = 1.20 / 1,452 = 13,77 = 13,77

- $y = (4/3) \cdot 13,77 / 1,452 = 12,8 = 12,65$

- $x = (5/3) \cdot 12,65 / 1,452 = 14,9 = 14,52$

- entrada, para conferir = 1.14,52 / 1.452 = 10 (ok)

#### (c) Atrasos individuais (d = gh + p):

- a.  $d inv = 1 \cdot (20/13,77) + 1 = 2,45$

- b. d nand = (4/3)(13,77/12,65) + 2 = 3,45

- c. d nor = (5/3) (12,65/14,52) + 2 = 3,45

- d. d inv = 1. (14,52/10) + 1 = 2,45

#### - Somando os atrasos individuais: 11,8 → confere!

#### QUESTÃO 22 – rede multi-estágio com derivação

- $G = 1 \cdot (4/3) \cdot (5/3) \cdot 1 = 20/9$

- B = 2 ← devido à derivação na nand

- H = 9

- F = GBH = 40

- **D** = N.F exp (1/N) + P = 4. (40) exp (1/4) + 6 =  $\frac{16,059}{1}$

- $f = (40) \exp(1/N) = 2,515$

- Dimensionamentos

- c = 1.9 / 2,51 = 3,58

- b = (5/3) . 3,57/2,51 = 2,37

- $c = (4/3) \cdot (2.2,37) / 2,51 = 2,51$

- inversor, conferindo: 1 . 2,51 / 2.51 = 1 (ok)

- Tempos (d = gh + p)

- d Inversor: = 1.(9/3,57) + 1 = 3,51

- d Nor = (5/3)(3,57/2,37) + 2 = 4,51

- d Nand = (4/3)(2\*2,37/2,51) + 2 = 4,51

- $d Inv = 1 \cdot (2.51/1) + 1 = 3.51$

- delay total =  $\frac{16,059}{100}$  unidades de tempo (ok)

#### QUESTÃO 23 – Solução da sequência de 8 nands 4:

$$G = 2^8 = 256$$

(G nand4 = 2)

$$B = 3^7 = 2187$$

$$H = 3$$

$$P = 8 * 4 = 32$$

$$F = GBH = 1.679.616$$

$$D = 8. (1.679.616) \exp(1/8) + 32 = 80$$

unidades de atraso

#### **QUESTÃO 24 - Dimensionamento ANDs**

|   | G    | В    | Н    | F=GBH | Р    | N    | D min | f    | у    |

|---|------|------|------|-------|------|------|-------|------|------|

| а | 1,33 | 1,00 | 6,00 | 8,00  | 3,00 | 2,00 | 8,66  | 2,83 | 2,12 |

| b | 1,67 | 1,00 | 6,00 | 10,00 | 3,00 | 2,00 | 9,32  | 3,16 | 3,16 |

#### **QUESTÃO 26 - Dimensionamento de um dado gate**

$$dA = 1 * (30/20) + 1 = 4$$

$$dB = (4/3) * (90/30) + 2 = 6$$

$$dC = (5/3) * (45/30) + 3 = 5,5$$

$$dD = (9/3) * (x/45) + 4 = x/15 + 4$$

$$dE = 1 * (200/x) + 1 = 200/x + 1$$

$$4+6+5,5+(x/15+1)+(200/x+1)=28$$

$$x/15 + 200/x - 7,5 = 0$$

$x^2 - 112,5x + 3000 = 0$

raiz 1 69,0586885 raiz 2 43,4413115

A escolha é pela solução 43,44 → menos área de silício

delays 5,603913

6,896087

5,5

6

4

28

#### QUESTÃO 27 – Opções de dimensionamento

|         | opção 1  | opção 2  |

|---------|----------|----------|

| G       | 5,333333 | 10       |

| В       | 2        | 1        |

| Н       | 40       | 40       |

| F (GBH) | 426,6667 | 400      |

| N       | 4        | 4        |

| atraso  | 27,17951 | 28,88854 |

| f       | 4,544877 | 4,472136 |

| d       | 264,03   | 89,44    |

| С       | 77,46    | 40,00    |

| b       | 45,45    | 26,83    |

| in      | 10,00    | 10,00    |

| área    | 396,94   | 166,28   |

## QUESTÃO 28 – inversores com carga 25 vezes na saída

$$D1 = 1 \cdot 25^{1} + 1 = 26$$

$$D2 = 3 \cdot 25^{1/3} + 3 = 11,772 \leftarrow \text{três tem o atraso mínimo}$$

$$D2 = 5 \cdot 25^{1/5} + 5 = 14,518$$

Contribuição de cada estágio:  $f = 25^{-1/3} = 2,92$  cada inversor deve ser 2,92 vezes maior no estágio seguinte.

$$N = log_4 F = log 25/log4 = 2,32 \rightarrow 3 estágios$$

#### QUESTÃO 29 – inversores com carga 800 vezes na saída

#### Solução da sequência de inversores→ cinco ESTÁGIOS tem o atraso mínimo

| carga |        | 800    | 5 está | igios    |

|-------|--------|--------|--------|----------|

|       | atraso |        | f =    | 3.807308 |

| 1     |        | 801.00 | Inv5   | 210.12   |

| 3     |        | 30.85  | Inv4   | 55.19    |

| 5 | 24.04 | Inv3 | 14.50 |

|---|-------|------|-------|

| 7 | 25.19 | Inv2 | 3.81  |

|   |       | Inv1 | 1.00  |

Cada inversor deve ser 3,8 vezes maior no estágio seguinte.