# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### ALEXANDRE DE MORAIS AMORY

## Lógica e Escalonamento de Teste para Sistemas com Redes Intra-Chip Baseadas em Topologia de Malha

Tese apresentada como requisito parcial para a obtenção do grau de Doutor em Ciência da Computação

Prof. Dr. Marcelo Lubaszewski Orientador

Prof. Dr. Fernando Gehm Moraes Co-orientador

## CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Amory, Alexandre de Morais

Lógica e Escalonamento de Teste para Sistemas com Redes Intra-Chip Baseadas em Topologia de Malha / Alexandre de Morais Amory. – Porto Alegre: Programa de Pós-Graduação em Computação, 2007.

178 f.: il.

Tese (doutorado)— Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR-RS, 2007. Orientador: Marcelo Lubaszewski; Co-orientador: Fernando Gehm Moraes.

1. Teste de sistemas intra-chip. 2. Lógica envoltória de teste. 3. Escalonamento de teste. 4. Redes intra-chip. I. Lubaszewski, Marcelo. II. Moraes, Fernando Gehm. III. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. José Carlos Ferraz Hennemann Vice-Reitor: Prof. Pedro Cezar Dutra Fonseca

Pró-Reitora de Pós-Graduação: Prof<sup>a</sup>. Valquíria Linck Bassani Diretor do Instituto de Informática: Prof. Flávio Rech Wagner

Coordenadora do PPGC: Prof<sup>a</sup>. Luciana Porcher Nedel

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **AGRADECIMENTOS**

O período do doutorado é longo e cansativo. Percorrer esse caminho com o apoio que tive certamente tornou a caminhada mais simples. Inicialmente gostaria de agradecer o apoio financeiro da Capes e CNPq; não agradeço somente a ajuda finaceira, mas também a oportunidade de fazer estágio no exterior, que realmente expandiu meus horizontes. Falando em novos horizontes no exterior, gostaria de agradecer a Erik Jan Marinissen e Kees Goossens da Philips Research Labs pela oportunidade e aprendizado.

Nao é por falta de imaginação, eu sei que já usei essa passagem de Gandhi antes, mas ainda não consegui achar uma passagem que representasse melhor o meu agradecimento aos meus orientadores Marcelo Lubaszewski e Fernando Moraes: "... I have always felt that the true text-book for the pupil is his teacher. I remember very little that my teachers taught me from books, but I have even now a clear recollection of the things they taught me independently of books". O conhecimento 'dos livros' é obviamente necessário para a conclusão do doutorado. Isso definitivamente recebi nas nossas inumeras discuções, brain-storms, e revisões de texto. Entretanto, o conhecimento técnico, principalmente nessa área ligado à tecnologia de ponta, fica defasado rapidamente. Porém, o ensinamento mencionado na frase de Gandi não deteriora. Pode passar muito tempo mas, mesmo que involuntariamente, ainda estarei usando esse conhecimento, e eventualmente passando adiante.

Doutarado muitas vezes envolve muito stress; isso é inevitável. Quem melhor para aliviar (ou melhor, evitar) esse stress do que com seus amigos, tomando uma cervejinha? Felizmente tive bons amigos para recorrer como: o Fabiano, amigo de longa data; o pessoal do GAPH: Ost <sup>1</sup>, Möller, Ewerson, Edson, e Castanha; o pessoal do GME: Gustavo, Lazzari, Edgard, Zé, Júlio, Paulo, Renato e Brião; People from Eindhoven: Tobias, Sylvain, Ram, Patrick, Vlado, Goran, Rodrigo, Samir, and Saurin; e mais recentemente tem o pessoal do CEITEC. Obrigado! vocês tornaram minha caminhada mais tranquila.

Muito bem, amigos ajudam e muito a aliviar/evitar stress. Mas e quando isso não é o suficiente? A quem recorrer nos momentos bons e também nos "não tão bons assim"? recorrer tanto na hora certa quanto na hora errada? No meu caso eu recorria as meninas da minha vida: Ariela, Duda, Camila, Leticia e Sonia. Tenho muito a agradeçer a elas. Não sei nem por onde começar. Sei que também tenho muito que me desculpar, principalente pela ausência pois essa coisinha chamada "Doutorado" consume muito. À Leticia, que esteve comigo esse tempo todo, obrigado pela paciência em aguentar meu mau humor! Obrigado pela ajuda! Obrigado pelo apoio! Obrigado pelo carinho! ... Obrigado por tudo! Enfim, terminou!

<sup>&</sup>lt;sup>1</sup>Viu só! não me esqueci de ti dessa vez !!! Não pude perder a oportunidade :-P

# **TABLE OF CONTENTS**

| LIST OF SYMBOLS  LIST OF FIGURES  LIST OF TABLES  LIST OF ALGORITHMS  ABSTRACT  RESUMO  1 INTRODUCTION  1.1 Problems to be Solved  1.2 Goals  1.3 Contribution    | . 13                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| LIST OF TABLES  LIST OF ALGORITHMS  ABSTRACT  RESUMO  1 INTRODUCTION  1.1 Problems to be Solved  1.2 Goals  1.3 Contribution                                      | . 10                                                                                    |

| LIST OF ALGORITHMS  ABSTRACT  RESUMO  1 INTRODUCTION  1.1 Problems to be Solved  1.2 Goals  1.3 Contribution                                                      | . 17                                                                                    |

| ABSTRACT                                                                                                                                                          | . 19                                                                                    |

| 1 INTRODUCTION          1.1 Problems to be Solved          1.2 Goals          1.3 Contribution                                                                    | . 21                                                                                    |

| 1 INTRODUCTION          1.1 Problems to be Solved          1.2 Goals          1.3 Contribution                                                                    | . 23                                                                                    |

| 1.1 Problems to be Solved          1.2 Goals          1.3 Contribution                                                                                            | . 25                                                                                    |

| 1.4Outline of the Thesis1.4.1Background, Definitions, and Models1.4.2DfT Design for NoC Reuse1.4.3Test Optimization                                               | <ul><li>. 31</li><li>. 32</li><li>. 32</li><li>. 32</li><li>. 32</li><li>. 32</li></ul> |

| 2 RELATED BACKGROUND          2.1 Modular Testing          2.2 Networks-on-Chip          2.2.1 Functional NoC Model          2.2.2 Some Industrial NoC Approaches | <ul><li>. 35</li><li>. 38</li><li>. 43</li></ul>                                        |

| 3 PRIOR WORK                                                                                                                                                      | <ul><li>. 49</li><li>. 51</li><li>. 55</li><li>. 56</li></ul>                           |

| 3.2.2 Dedicated Bus-Based Access                                                                                                                                  | . 59<br>. 59                                                                            |

| 3.4.3 | Programmable On-Chip Tester                        | <br> |   | 61  |

|-------|----------------------------------------------------|------|---|-----|

| 3.5   | Other Relevant Test Approaches                     |      |   | 63  |

| 3.5.1 | NoC Testing                                        | <br> |   | 63  |

| 3.5.2 | FIFO Testing                                       | <br> |   | 64  |

| 3.5.3 | Interconnect Testing                               | <br> |   | 66  |

| 3.6   | Discussion                                         | <br> |   | 67  |

| 4 P   | ROPOSED TEST MODEL                                 | <br> |   | 69  |

| 4.1   | Fundamental Hypotheses                             | <br> |   | 69  |

| 4.2   | Properties of Proposed Test Model                  | <br> |   | 70  |

| 4.3   | Test Traffic Requirements                          | <br> |   | 70  |

| 4.4   | Sources of Jitter in NoCs                          | <br> |   | 71  |

| 4.4.1 | Shared Channels                                    | <br> |   | 71  |

| 4.4.2 | Shared Routers                                     | <br> |   | 71  |

| 4.4.3 | Load Fluctuation                                   | <br> |   | 71  |

| 4.5   | Introduction to the Proposed Model                 | <br> |   | 72  |

| 4.5.1 | ATE Interface                                      | <br> |   | 72  |

| 4.5.2 | Test Wrapper                                       | <br> |   | 72  |

| 4.5.3 | The NoC Partition Method                           | <br> |   | 73  |

| 4.5.4 | More Examples about the NoC Partition Approach     | <br> |   | 74  |

| 4.6   | Reducing the Jitter Bound Using NoC Partitioning . | <br> |   | 75  |

| 4.6.1 | Shared Channels and Routing Logic                  | <br> |   | 77  |

| 4.6.2 | Load Fluctuation                                   | <br> |   | 77  |

| 4.7   | Overall Problem Statement                          |      |   | 77  |

| 4.8   | Proposed Design Flow                               | <br> |   | 80  |

| 4.9   | Comparison with Previous Approaches                | <br> |   | 80  |

| 4.10  | Summary                                            | <br> | • | 82  |

| 5 T   | EST WRAPPERS FOR CORES                             | <br> |   | 85  |

| 5.1   | Problem Statement                                  | <br> |   | 85  |

| 5.2   | Wrapper Design Overview                            |      |   |     |

| 5.3   | Wrapper Design and Optimization                    | <br> |   | 88  |

| 5.3.1 | Core Terminal Classification                       | <br> |   | 88  |

| 5.3.2 | Wrapper Cell Design and Assignment                 | <br> |   | 89  |

| 5.3.3 | Partitioning and Ordering of Wrapper Chain Items   |      |   | 91  |

| 5.3.4 | NoCs With and Without Guaranteed Services          |      |   | 93  |

| 5.4   | Experimental Results                               |      |   | 94  |

| 5.4.1 | Simplified Illustrative Example                    |      |   | 94  |

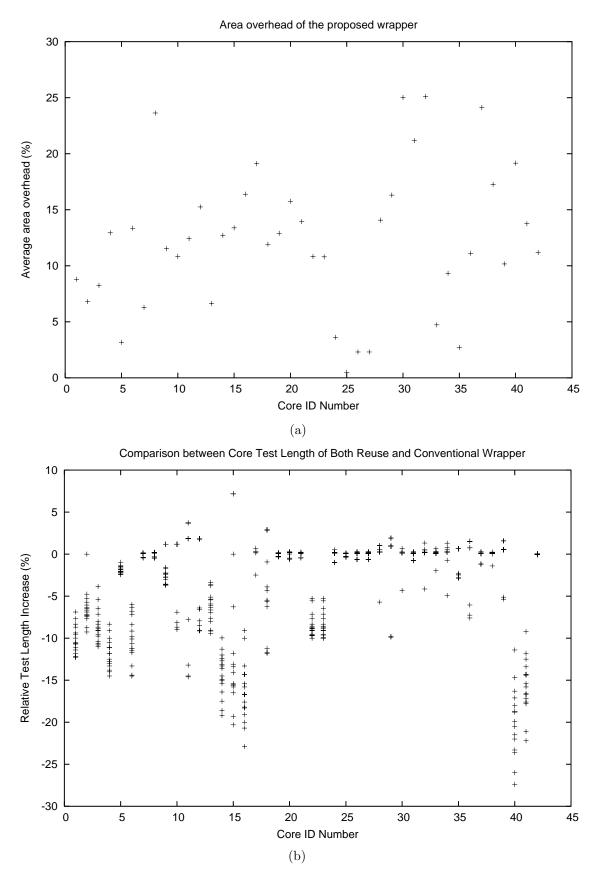

| 5.4.2 | Wrapper Area and Core Test Length Impact           |      |   | 95  |

| 5.4.3 | Wrapper Area for NoCs Without Guaranteed Services  |      |   | 97  |

| 5.5   | Discussion                                         |      |   | 97  |

| 5.6   | Summary                                            | <br> |   | 100 |

| 6 D   | FT FOR SOURCES AND SINKS                           |      |   |     |

| 6.1   | Reuse of Embedded Processors                       |      |   |     |

| 6.1.1 | Results                                            | <br> |   | 104 |

| 6.1.2 | Discussion                                         |      |   |     |

| 6.2   | ATE Interface                                      |      |   |     |

| 6.2.1 | ATE Interface in the Proposed Design Flow          | <br> |   | 105 |

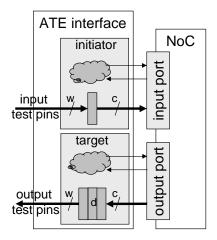

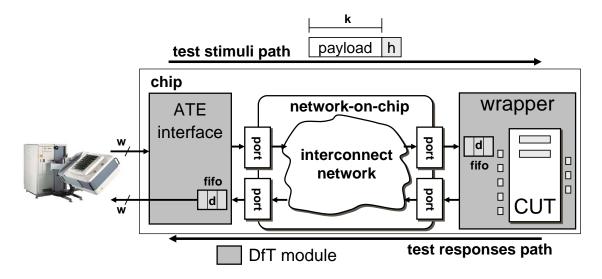

| 6.2.2 | Functional Description of the ATE Interface                | . 106 |

|-------|------------------------------------------------------------|-------|

| 6.2.3 | Block Diagram of the ATE Interface                         | . 107 |

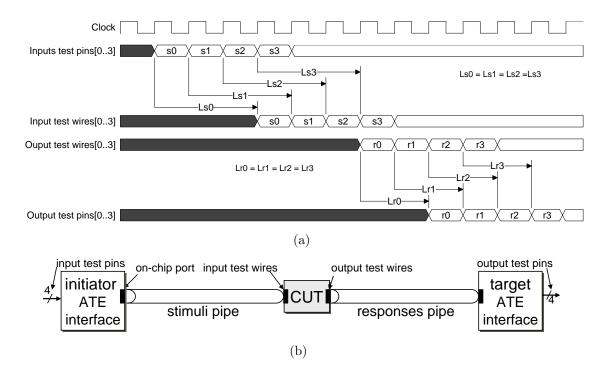

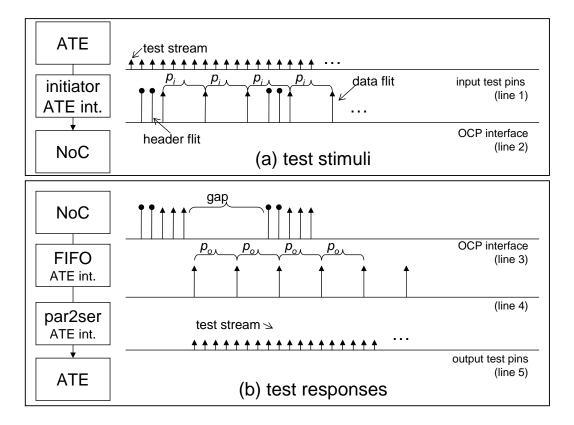

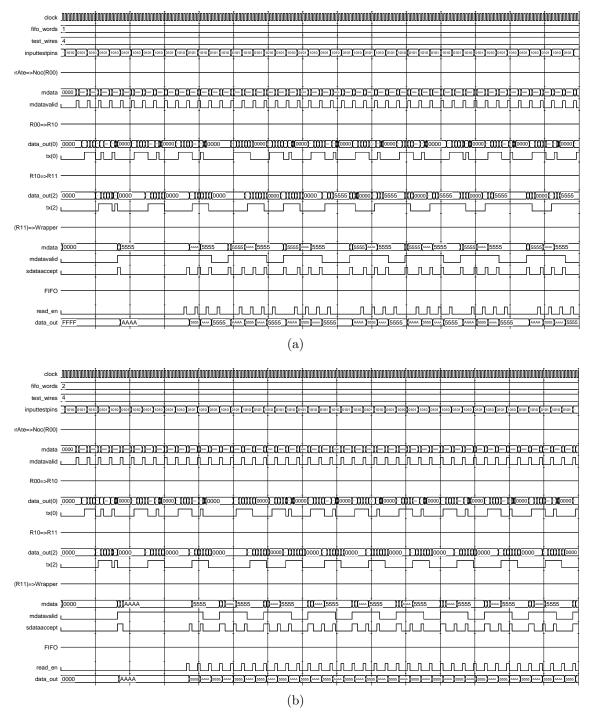

| 6.2.4 | Timing Diagram of the ATE Interface                        |       |

| 6.2.5 | Integrating the ATE Interface to the SoC                   | . 107 |

| 6.2.6 | Synthesis Results                                          | . 110 |

| 6.2.7 | Discussion                                                 | . 110 |

| 6.3   | Summary                                                    | . 112 |

| 7 D   | FT FOR NETWORKS-ON-CHIP                                    | . 113 |

| 7.1   | Introduction                                               | . 113 |

| 7.2   | Case Study: the SoCIN Network                              | . 114 |

| 7.3   | Main Challenges                                            | . 114 |

| 7.4   | Evaluating Standard Test Strategies in NoCs                | . 115 |

| 7.5   | Proposed Test Strategy for NoCs Based on Identical Routers | . 117 |

| 7.5.1 | Router Testing                                             | . 117 |

| 7.5.2 | NoC Testing                                                | . 117 |

| 7.5.3 | Test Wrapper for NoCs                                      | . 119 |

| 7.6   | Experimental Results                                       | . 120 |

| 7.7   | Limitations                                                | . 122 |

| 7.8   | Summary                                                    | . 123 |

| 8 T   | EST SCHEDULING                                             | . 125 |

| 8.1   | Problem Statement                                          | . 125 |

| 8.2   | Proposed Test Strategy                                     | . 127 |

| 8.2.1 | Previous Test Scheduling Algorithm                         | . 127 |

| 8.2.2 | Employed Data Structure                                    | . 127 |

| 8.2.3 | The Proposed Algorithm                                     | . 128 |

| 8.2.4 | Minimizing Test Length and Silicon Area                    | . 134 |

| 8.3   | Results                                                    | . 134 |

| 8.3.1 | Experimental Setup                                         | . 134 |

| 8.3.2 | Introduction to Relevant Variables                         | . 135 |

| 8.3.3 | Experiment Model                                           | . 135 |

| 8.3.4 | Definitions                                                | . 137 |

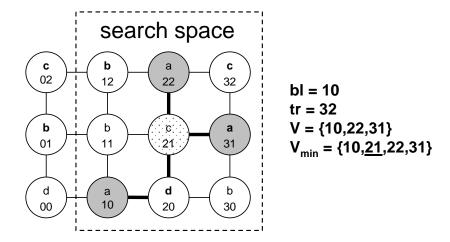

| 8.3.5 | Pruning Search Space                                       | . 137 |

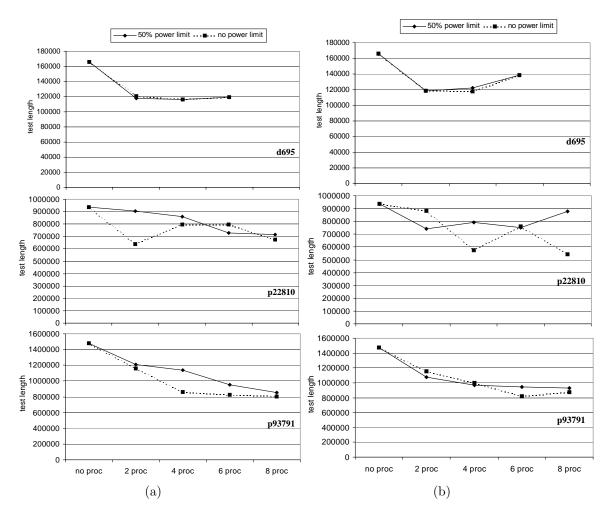

| 8.3.6 | Main Results                                               | . 139 |

| 8.3.7 | Illustrative Example                                       | . 140 |

| 8.3.8 | Estimating Wire Length Savings                             |       |

| 8.4   | Discussion                                                 | . 146 |

| 8.5   | Limitations                                                |       |

| 8.6   | Summary                                                    | . 147 |

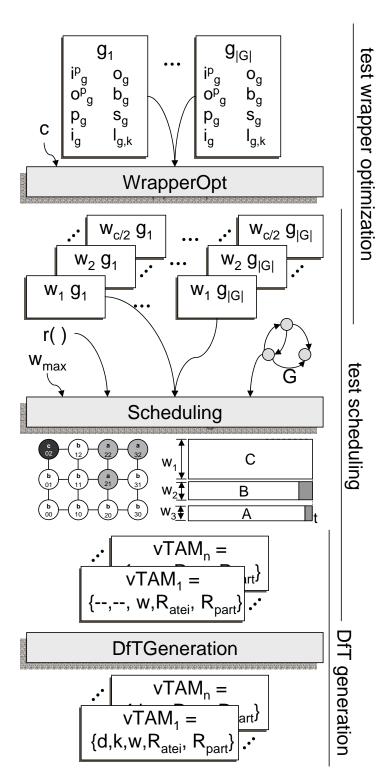

| 9 D   | FT OPTIMIZATION AND GENERATION                             | . 149 |

| 9.1   | Proposed Algorithm for Buffer Sizing                       | . 149 |

| 9.2   | Results                                                    | . 150 |

| 9.3   | Discussion                                                 | . 151 |

| 9.4   | Summary                                                    | . 151 |

| <b>10 CONCLUSION</b>                                           |

|----------------------------------------------------------------|

| <b>10.1</b> Qualitative Analysis                               |

| 10.1.1 Toward a General NoC-Reuse Approach                     |

| 10.1.2 Compatibility with Conventional SoC Modular Testing 153 |

| 10.1.3 Detailed DfT Design                                     |

| 10.1.4 Comparison with Conventional Test Architecture          |

| <b>10.2</b> Quantitative Analysis                              |

| 10.2.1 SoC Test Length                                         |

| 10.2.2 Silicon Area for DfT Modules                            |

| <b>10.3</b> Prospected Impact                                  |

| 10.4 Accomplished Goals and Contribution                       |

| 10.5 Limitations and Issues Not Addressed                      |

| <b>10.6</b> Future Work                                        |

| <b>REFERENCES</b>                                              |

| <b>APPENDIX A</b>                                              |

| <b>APPENDIX B</b>                                              |

## LIST OF ABBREVIATIONS AND ACRONYMS

ASIC Application-Specific Integrated Circuit

ATE Automatic Test Equipment

ATPG Automatic Test Pattern Generation

AXI Advanced eXtensible Interface

BE Best-Effort

BIST Built-in Self-Test

CUT Core-Under-Test

DfT Design-for-Test

DSM Deep Sub-Micron

DTL Device Transaction Level

FIFO First-In First-Out

GT Guaranteed Throughput

IP Intellectual Property

LFSR Linear feedback Shift Register

MISR Multiple Input Signature Register

NI Network Interface

NoC Network-on-Chip

OCP Open Core Protocol

QoS Quality of Service

SoC System-on-Chip

TAM Test Access Mechanism

TRP Test Resource Partition

UDL User-Defined Logic

vTAM virtual Test Access Mechanism

# LIST OF SYMBOLS

| $i_g^p$    | the input test port of the module $g$ . Page 77.                                            |

|------------|---------------------------------------------------------------------------------------------|

| $O_g^p$    | the output test port of the module $g$ . Page 77.                                           |

| $p_g$      | the number of test patterns of the module $g$ . Page 77.                                    |

| $i_g$      | the number of functional input terminals of the module $g$ . Page 77.                       |

| $o_g$      | the number of functional output terminals of the module $g$ . Page 77.                      |

| $b_g$      | the number of functional bidirectional terminals of the module $g$ . Page 77.               |

| $s_g$      | the number of scan chains of the module $g$ . Page 77.                                      |

| $l_{g,k}$  | the scan length of the scan $k$ of the module $g$ . Page 77.                                |

| $f_g$      | the number of scan flip-flops of the module $g$ . Page 77.                                  |

| $w_{max}$  | the maximal number of test wires assigned for the test scheduling. Page 77.                 |

| c          | the physical channel width of the NoC. Page 77.                                             |

| r()        | the routing algorithm used by the NoC. Page 77.                                             |

| vTAM       | the tuple $\{d, k, w, R_{atei}, R_{part}\}$ . Page 77.                                      |

| d          | the FIFO depth assigned to the ATE interfaces and wrappers in this vTAM. Page 77.           |

| k          | the packet size used to send test stimuli. Page 77.                                         |

| w          | the number of test wires assigned to the ATE interfaces and wrappers in this vTAM. Page 77. |

| $R_{atei}$ | the set of ATE interfaces in a given vTAM. Page 77.                                         |

| $R_{part}$ | the set of routers in a given vTAM. Page 77.                                                |

|            |                                                                                             |

the parallel-to-serial loading and serial-to-parallel unloading time of

the parallel-to-serial loading and serial-to-parallel unloading time of

tuple  $\{tw, d, V\}$ . Page 105.

the stimuli path. Page 86.

the responses path. Page 86.

ATE interface

$p_i$

$p_o$

$c_i$  the number of data bits that comes from the NoC to the DfT mod-

ule. Page 86.

$c_o$  the number of data bits that goes from the DfT module to the NoC.

Typically  $c_i = c_o = c$ . Page 86.

SDI the set of selected data input terminals of an input test port. Page 88.

SDO the set of selected data output terminals of an output test port.

Page 88.

RSDI the set of remaining selected data input terminals of an input test

port. Page 88.

RSDO the set of remaining selected data output terminals of an output

test port. Page 88.

DI the set of data input terminals of a test port. Page 88.

DO the set of data output terminals of a test port. Page 88.

CI the set of control inputs of a test port. Page 88.

the set of control outputs of a test port. Page 88.

$DI_{in}$  the set of data input terminals of the input test port. Page 88.

$DO_{in}$  the set of data output terminals of the input test port. Page 88.

$CI_{in}$  the set of control inputs of the input test port. Page 88.

$CO_{in}$  the set of control outputs of the input test port. Page 88.

DI<sub>out</sub> the set of data input terminals of the output test port. Page 88.

$DO_{ou}$  the set of data output terminals of the output test port. Page 88.

CI<sub>out</sub> the set of control inputs of the output test port. Page 88.

$CO_{out}$  the set of control outputs of the output test port. Page 88.

FI the set of all functional input terminals that are not part of the

selected test ports. Page 88.

FO the set of all functional output terminals that are not part of the

selected test ports. Page 88.

SI the set of scan-in terminals. Page 88.

the set of scan-out terminals. Page 88.

WC\_SD1\_COI the 'regular' wrapper cell. Page 89.

WC\_SD1\_COI\_G the guarded wrapper cell. Page 89.

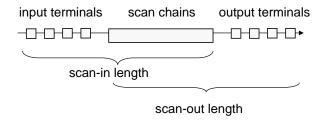

$s_i$  scan-in length. Page 91.

$s_o$  scan-out length. Page 91.

$T_{conv}$  conventional core test length. Page 91.

$t_i$  scan-in time. Page 92.

$t_o$  scan-out time. Page 92.

$T_{new}$  proposed core test length. Page 92.

$b_{test}$  maximal supported bandwidth of a given wrapper. Page 93.

$b_o^{out}$  maximal supported output bandwidth of the output port. Page 93.  $b_i^{in}$  maximal supported input bandwidth of the input port. Page 93.

$w^{max}$  maximal supported number of test wires of a given wrapper. Page 93.

V a set of the tuple  $\{nburst, header, nword\}$ . Page 105.

nburst the number of test packets to send the test set. Page 105.

header the header content of each test packet. Page 105.

nword the number of flits of each test packet. Page 105.

$P_g$  the Pareto curve of a core g. Page 125.

# LIST OF FIGURES

| Figure 1.1: | Projected relative delay for wires and logic gates                   | 28 |

|-------------|----------------------------------------------------------------------|----|

| Figure 1.2: | Evolution of communication architectures                             | 28 |

| Figure 1.3: | Comparison between communication architectures                       | 29 |

| Figure 2.1: | general conceptual test architecture                                 | 35 |

| Figure 2.2: | Example of TestRail architecture and test schedule                   | 36 |

| Figure 2.3: | Core test length for non-preemptive and preemptive test              | 37 |

| Figure 2.4: | Core test length vs. bandwidth                                       | 38 |

| Figure 2.5: | A simple NoC instance                                                | 39 |

| Figure 2.6: | A typical router architecture                                        | 39 |

| Figure 2.7: | Examples of physical channel flow control                            | 40 |

| Figure 2.8: | Latency from the source to the destination                           | 41 |

| Figure 2.9: | Protocol layers and the main building blocks of a NoC-based design.  | 42 |

| Figure 2.10 | : Initiator and target ports; read and write transactions            | 43 |

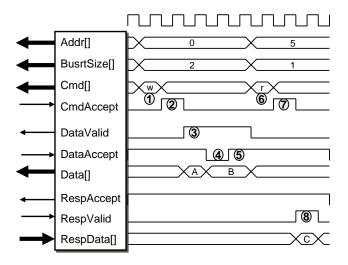

| Figure 2.11 | : Protocol of an OCP-like port                                       | 44 |

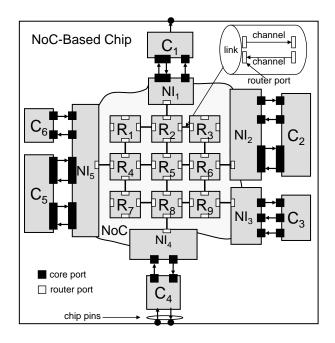

| Figure 2.12 | : A more complex NoC instance.                                       | 45 |

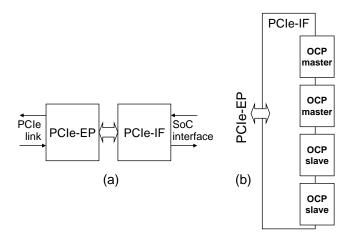

| Figure 2.13 | : Block diagram of the PCI Express IP core                           | 46 |

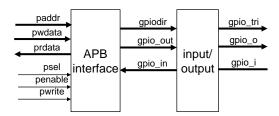

| Figure 2.14 | : Block diagram of the GPIO IP core                                  | 46 |

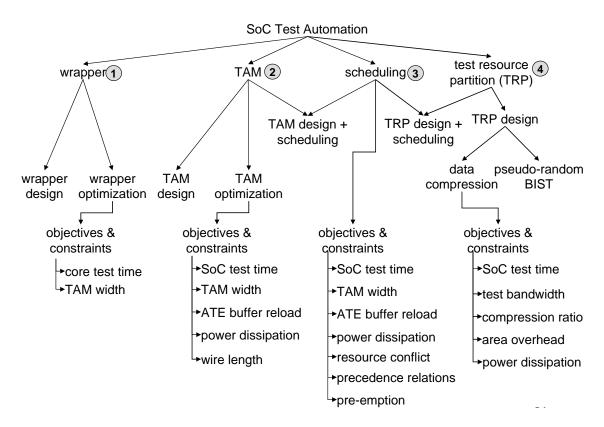

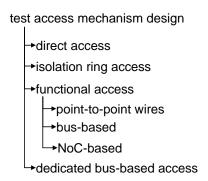

| Figure 3.1: | Classification of problems in SoC test field                         | 50 |

| Figure 3.2: | Relation among the surveyed problems and the addressed problems.     | 50 |

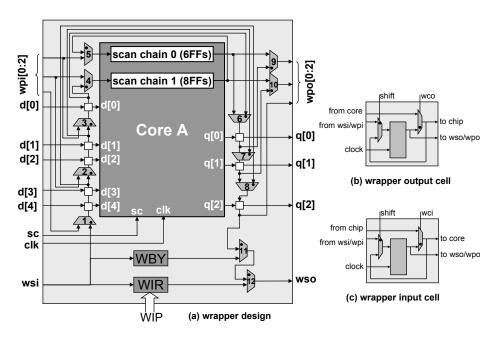

| Figure 3.3: | IEEE Std. 1500 wrapper architecture                                  | 52 |

| Figure 3.4: | IEEE Std. 1500 wrappers at the top-level                             | 53 |

| Figure 3.5: | Example of an IEEE Std. 1500 compliant wrapper                       | 53 |

| Figure 3.6: | IEEE Std. 1500 wrapper's test mode                                   | 54 |

| Figure 3.7: | Scan-in and scan-out lengths of wrapper elements                     | 56 |

| Figure 3.8: | LPT algorithm used to optimize test wrappers                         | 56 |

| Figure 3.9: | Classification of TAM designs                                        | 57 |

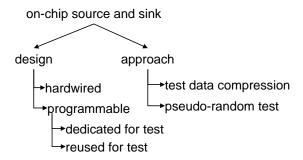

| Figure 3.10 | : Classification of on-chip ATE approaches                           | 60 |

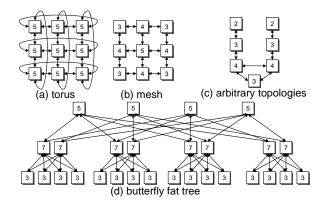

| Figure 3.11 | : Different network topologies and their degree                      | 64 |

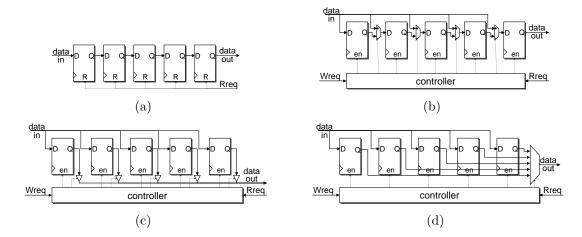

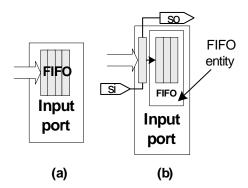

| Figure 3.12 | : FIFO designs                                                       | 65 |

| Figure 4.1: | Example of load fluctuation in an input test path                    | 72 |

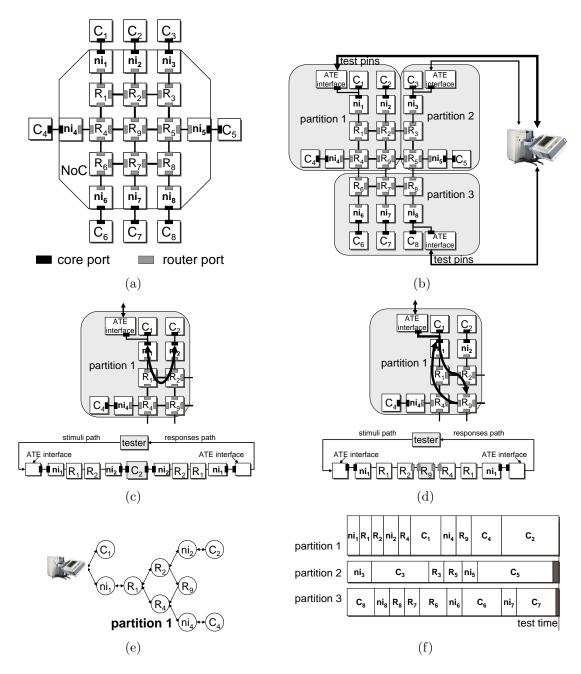

| Figure 4.2: | Example of partitioned NoC                                           | 74 |

| Figure 4.3: | Test model based on NoC partition                                    | 76 |

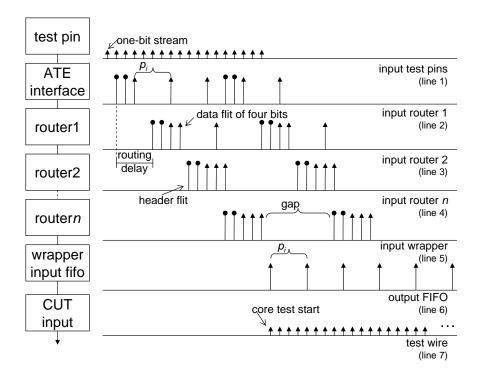

| Figure 4.4: | NoC abstracted as a pipeline and the required test data timing       | 77 |

| Figure 4.5: | Design flow in terms of the variables used in the problem statement. | 79 |

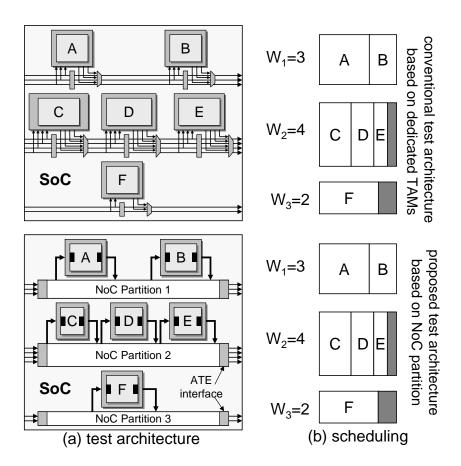

| Figure 4.6: | Comparing conventional and proposed test architectures               | 83 |

|             |                                                                      |    |

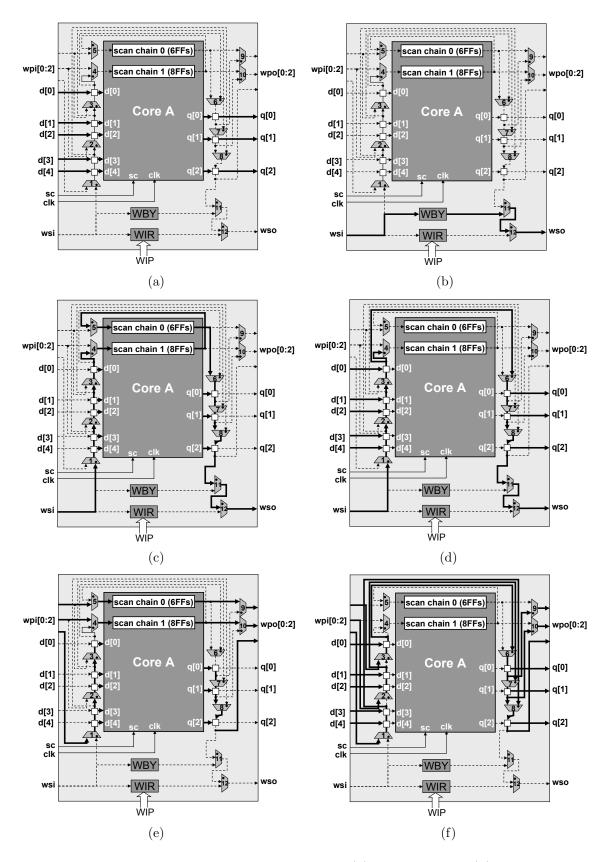

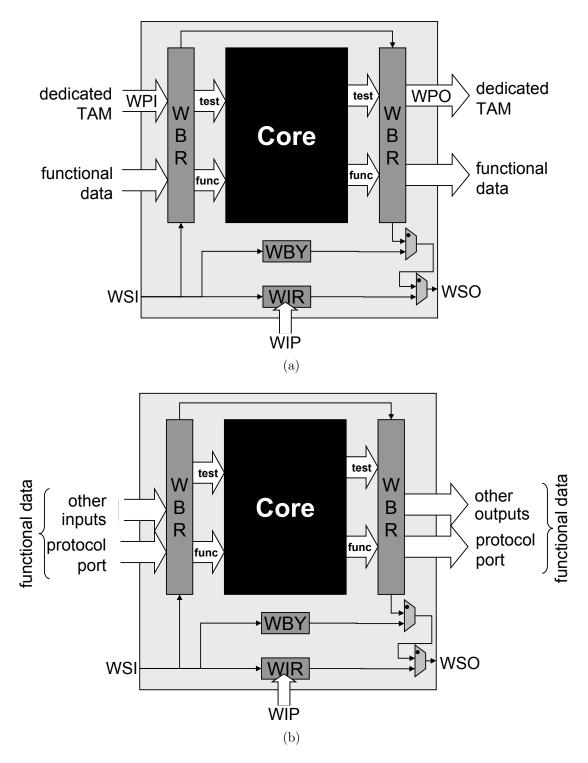

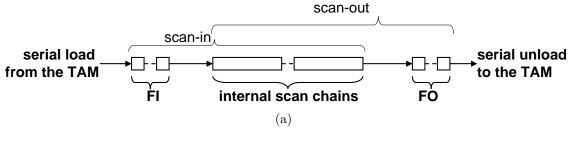

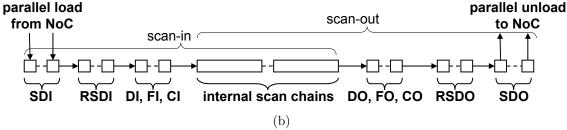

| Figure  | 5.1: | Overview of the (a) conventional and (b) new IEEE Std. 1500              |

|---------|------|--------------------------------------------------------------------------|

| T:      | r 0. | compliant wrapper design                                                 |

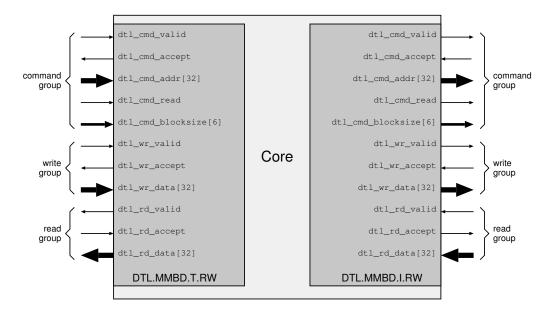

| Figure  |      | Example core with two DTL read-write ports                               |

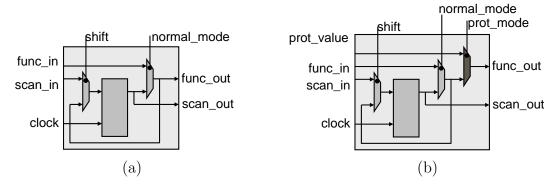

| Figure  |      | Implementation of wrapper cells                                          |

| Figure  |      | The order of wrapper items per wrapper chain                             |

| Figure  |      | Detailed wrapper design                                                  |

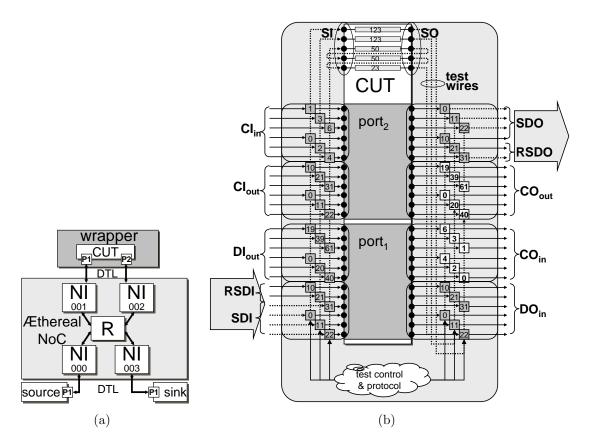

| Figure  |      | Wrapper waveform                                                         |

| Figure  | 5.7: | Comparing the proposed with the conventional wrapper design 101          |

| Figure  | 6.1: | Test length with different number of reused processors 104               |

| Figure  |      | Block diagram of the ATE interface                                       |

| Figure  |      | Timing diagram of the ATE interface                                      |

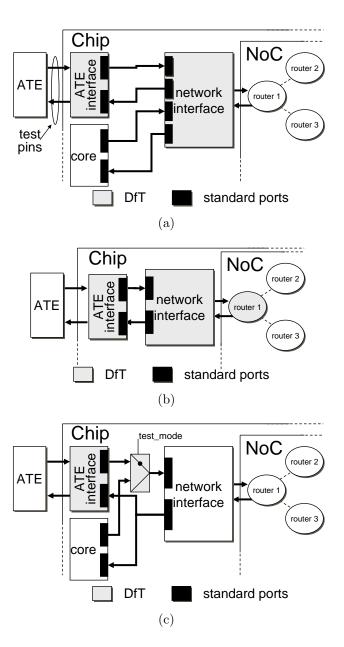

| Figure  |      | Alternatives to the ATE interface design                                 |

| Figure  |      | Interface of the ATE interface                                           |

| Figure  |      | Long wires required to connect the test pins to the ATE interface. 112   |

| 1 18410 | 0.0. | zong whee required to commerce the test plans to the 1112 interface. 112 |

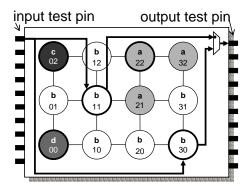

| Figure  | 7.1: | Splitting the input FIFOs: (a) original and (b) modified for testing.118 |

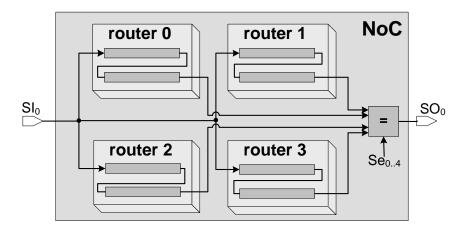

| Figure  | 7.2: | Testing multiple identical routers                                       |

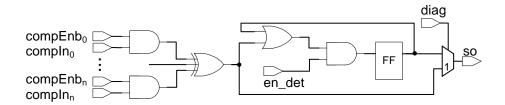

| Figure  | 7.3: | Comparator block                                                         |

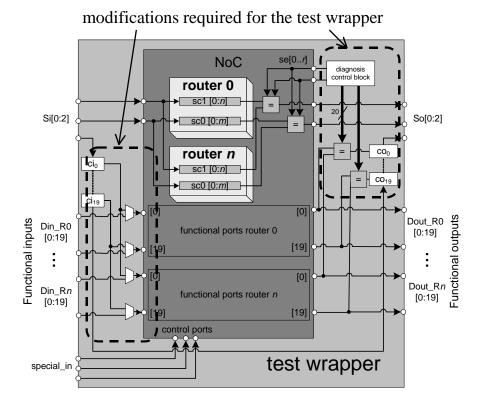

| Figure  | 7.4: | Proposed test wrapper for NoCs                                           |

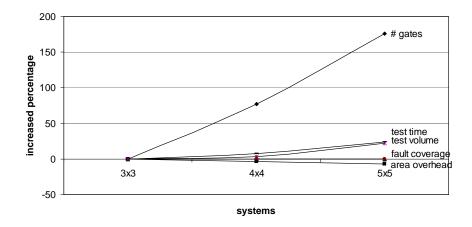

| Figure  | 7.5: | Test costs versus NoC silicon area                                       |

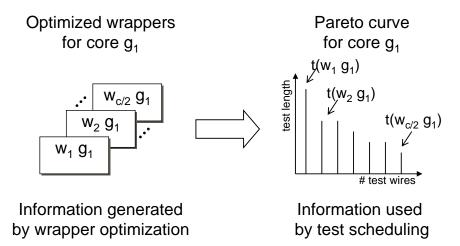

| Figure  | 8.1: | Building Pareto curve for the test scheduling                            |

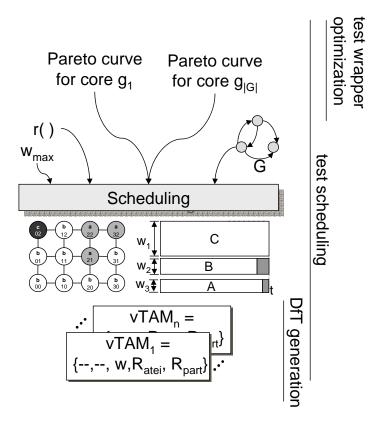

| Figure  |      | Scheduling design flow                                                   |

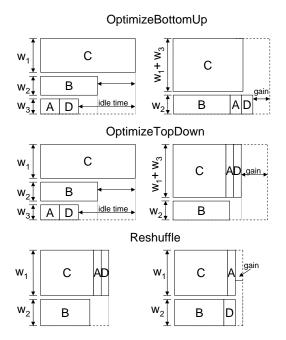

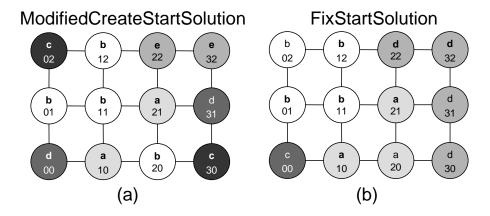

| Figure  |      | Illustrative example of the original optimization algorithms 128         |

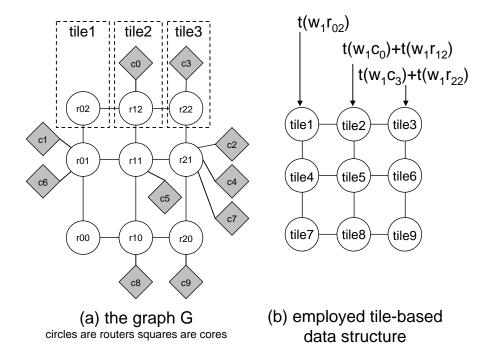

| Figure  |      | Transforming the input system in to the employed data structure. 129     |

| Figure  |      | Example of the FixStartSolution                                          |

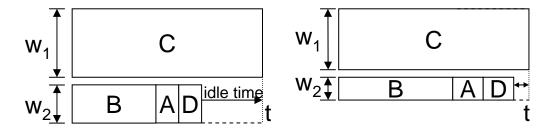

| Figure  |      | Example of optimization caused by OptimizeTestWires 133                  |

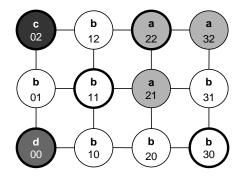

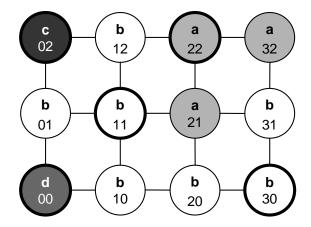

| Figure  |      | Example of a partitioned NoC                                             |

| Figure  |      | Flow of an experiment for each SoC                                       |

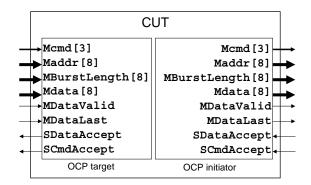

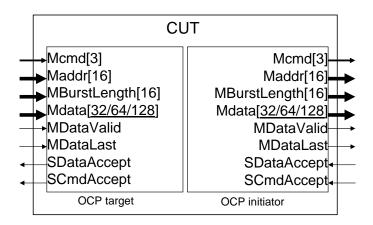

| Figure  |      | OCP port used in the experiments                                         |

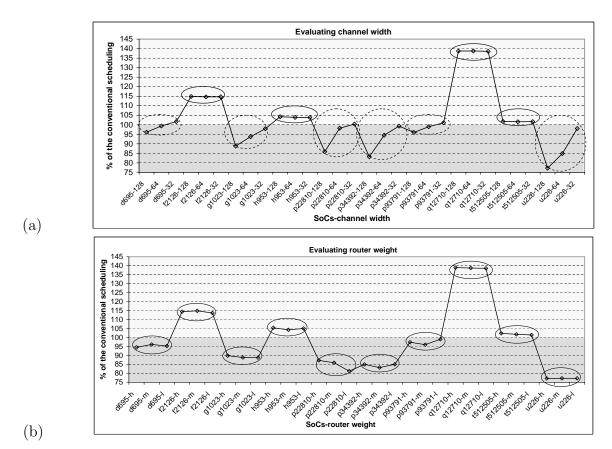

| 0       |      | Evaluating channel width and router weight on the SoC test length.138    |

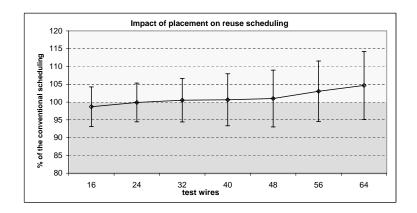

| _       |      | Impact of the placement on SoC test length                               |

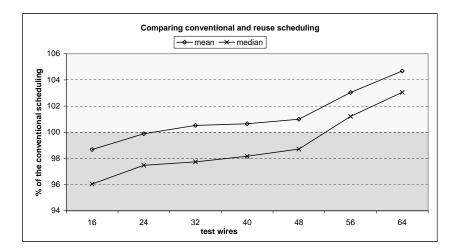

|         |      | Comparing conventional and NoC reuse test length                         |

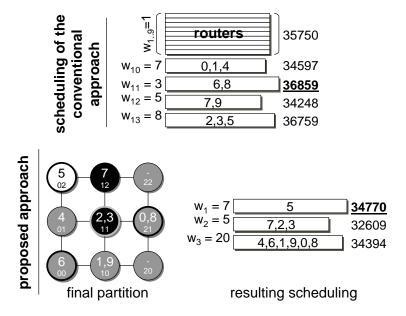

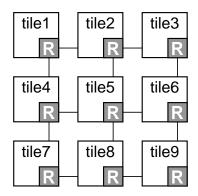

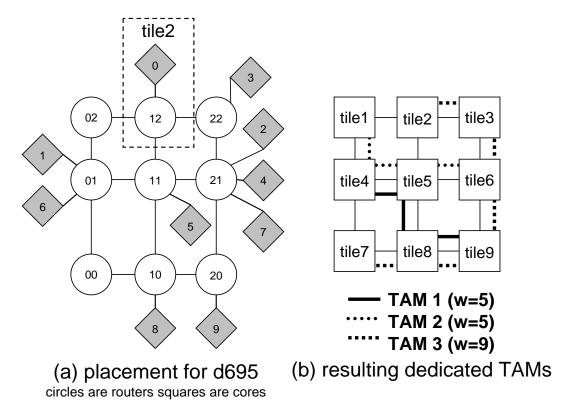

| _       |      | Example of both schedulings for the d695 SoC                             |

| 0       |      | NoC-based system modeled as regular tiles                                |

| _       |      | Estimated wire length required to create the dedicated TAMs 143          |

| _       |      | Minimum rectilinear steiner tree algorithm                               |

| Ü       |      |                                                                          |

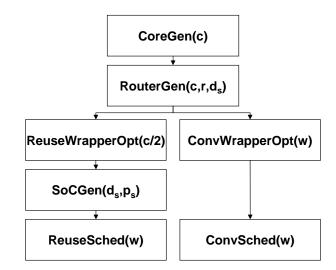

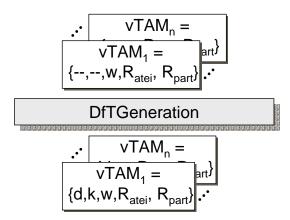

|         |      | DfT generation step                                                      |

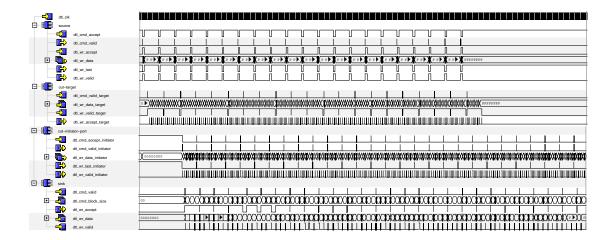

| Figure  |      | Conceptual simulation environment                                        |

| Figure  | 9.3: | Waveform of the simulation environment                                   |

# LIST OF TABLES

| Table 1.1:                                                                       | Comparison between bus and network                                                                           |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Table 3.1:<br>Table 3.2:<br>Table 3.3:                                           | Multiplexer configuration for each test mode                                                                 |

| Table 5.1:<br>Table 5.2:<br>Table 5.3:<br>Table 5.4:<br>Table 5.5:<br>Table 5.6: | Example classification of port terminals                                                                     |

| Table 6.1:                                                                       | Area of the ATE interface compared to a wrapper                                                              |

| Table 7.1:<br>Table 7.2:<br>Table 7.3:                                           | Comparing the RASoC router and the Plasma processor 115 Standard test strategies applied to a 3x3 NoC        |

| Table 8.1:<br>Table 8.2:<br>Table 8.3:<br>Table 8.4:                             | Extended results with the SoCs set up to $c=128$ and $r=medium$ . 141 Average wire length for dedicated TAMs |

# LIST OF ALGORITHMS

| Algorithm 6.1: | Initiator ATE Interface                |

|----------------|----------------------------------------|

| Algorithm 6.2: | Target ATE Interface                   |

| Algorithm 8.1: | Main Scheduling Algorithm              |

| Algorithm 8.2: | FixStartSolution                       |

| Algorithm 8.3: | ModifiedReshuffle                      |

| Algorithm 8.4: | OptimizeTestWires                      |

| Algorithm 8.5: | FindATEInterfaces                      |

| Algorithm 8.6: | $HalfPerimeter(V) \dots 143$           |

| Algorithm 8.7: | Minimum Rectilinear Steiner Tree $(V)$ |

| Algorithm 9.1: | Minimize Buffer $Size(w)$              |

### **ABSTRACT**

With the advance of microchip technology, global and long wires will cost more in terms of delay than in terms of logic gates. In addition, long wires are more susceptible to signal integrity problems such as crosstalk. A recently proposed global interconnect called network-on-chip alleviates the limitation of long wires. Moreover, on-chip networks allow decoupling communication and computation to divide a complete system into manageable and independent sub tasks. Thus, it is possible to integrate more logic into the chip using network-on-chip. However, the complexity growth of cores also increases the test costs since more logic is embedded into a single chip. These embedded cores need a test access mechanism for test data transportation, typically implemented as test-dedicated buses. As mentioned before, global wires are expensive, then, adding test buses may not be feasible in the near future. On the other hand, the on-chip network has access to most cores of the chip. This network could be used also for test data transportation, avoiding additional test-dedicated buses.

The goal of this thesis is to study the reuse of on-chip networks for test data transportation, looking for a general reuse approach that can be easily used in a given network. To reach this goal, the thesis is divided in three parts: models, design, and optimization. This thesis proposes a functional model of a network, compatible with most recently proposed best-effort on-chip networks. Based on this functional model, a test model is devised. The test model comprises of a set of necessary and sufficient information required to optimize the test architecture. The test architecture consists of DfT logic and scheduling algorithm. The design of DfT logic comprises adaptation logic for the external tester and test wrappers for the modules. The optimization procedure, focused on mesh-based best-effort NoCs, schedules test data such that the chip test length and DfT silicon area are minimized.

A conventional SoC test architecture based on test-dedicated buses is compared to the proposed approach for best-effort NoCs. The experimental results show that SoC test length has increased 5% on average. The results have also shown that the area overhead for proposed DfT is around +20% compared to the silicon area to implement the DfT of a conventional test architecture. On the other hand, we have also presented a simpler design flow and 20% to 50% of global wiring savings due to the use of NoC for test data transportation. The results corroborate with the conclusion that the proposed NoC reuse is a good approach for complex systems based on a large number of cores and routers.

**Keywords:** Modular Testing, System-on-Chip Testing, Core-Based Testing, Test Wrapper, Test Scheduling, Networks-on-Chip.

#### Lógica e Escalonamento de Teste para Sistemas com Redes Intra-Chip Baseadas em Topologia de Malha

## **RESUMO**

Com o avanço da tecnologia de fabricação de chips o atraso em fios globais será maior que o atraso em portas lógicas. Além disso, fios globais longos são mais suscetíveis a problemas de integridade como crosstalk. Uma proposta recente de interconnecção global chamada redes intra-chip reduz essas limitações referentes a fios longos. Além dessas vantagens, redes intra-chip permitem desacoplar comunicação e computação, dividindo um sistema em sub tarefas independentes. Devido as essas vantagens é possível integrar mais lógica em um chip que usa redes intra-chip. Entretanto, o acréscimo de lógica no chip aumenta o custo de teste. Os módulos do chip precisam de mecanismos para transportar dados de teste, que são tipicamente barramentos usados exclusivamente para teste. Entretanto, como mencionado anteriormente, fios globais são caros e acrescentar barramentos de teste pode não ser possível em um futuro próximo. Por outro lado, uma rede intra-chip tem acesso a maioria dos módulos do chip. Esta rede pode ser usada para transportar dados de teste, evitando o acréscimo de barramentos dedicados ao teste.

O objetivo dessa tese é estudar o uso de redes intra-chip para o transporte de dados de teste, enfatizando uma abordagem genérica que possa ser aplicada a uma dada rede. Para tanto, essa tese foi divida em três partes: modelos, projeto, e otimização. A tese propõe um modelo funcional de rede que é compatível com a maioria das recém propostas redes intra-chip. O modelo de teste, baseado no modelo funcional da rede, compreende o conjunto de informações necessárias para otimizar a arquitetura de teste. A arquitetura de teste, por sua vez, consiste de lógica para teste e algoritmo de otimização. A lógica de teste compreende lógica para ATE interface e lógica envoltória para módulos de hardware. Os algoritmos otimizam o tempo de teste e a área de lógica de teste no nível dos módulos e no nível do chip.

Uma arquitetura convencional de teste de SoCs baseada em barramento de teste dedicado foi comparada com a arquitetura proposta para SoCs baseados em redes intra-chip. Os resultados apontam que o tempo de teste do SoC com a arquitetura proposta aumenta em média 5%. Os resultados também mostram que a lógica de teste da arquitetura proposta é cerca de 20% maior que na arquitetura de teste convencional. Por outro lado, o fluxo de projeto baseado na arquitetura de teste proposta é mais simples que a convencional. Além disso, a arquitetura proposta reduz o número de fios globais em torno de 20% a 50% para SoCs complexos. Estes resultados demonstram que a arquitetura proposta é melhor para sistemas complexos com um grande número de módulos.

Palavras-chave: teste de sistemas intra-chip, lógica envoltória de teste, escalonamento de teste, redes intra-chip.

## 1 INTRODUCTION

The scaling of micro chip technology enables more logic, or an entire system, embedded in a single chip (System-on-Chip - SoC). It creates the opportunity to design tightly coupled parallel applications for example, for embedded systems in a portable device. However, it also brings challenges in terms of design productivity, design of global interconnect, and test for manufacturing defects (KEUTZER et al., 2000; ZORIAN; MARINISSEN; DEY, 1998).

The exponential shrink of the transistor size increases the available resources in a chip and increases the design complexity since more modules are embedded in the chip. In addition, the market competition demands a shorter design cycle. This motivates the adoption of some practices to deal with the design complexity, such as, core reuse, design partition, decoupling communication and computation, and higher levels of abstraction. The system is partitioned in independent sub tasks to ease its design and verification. These independent tasks rely on decoupling communication and computation to avoid the interference of other tasks. With independent tasks, higher levels of abstraction can be used to help the design. Moreover, the tasks are designed with standard interfaces to ease their integration. The system usually follows a layered design methodology to abstract the global interconnect implementation.

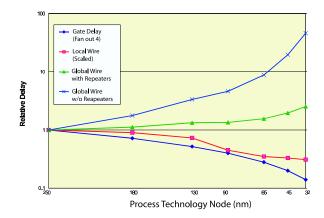

Another challenge of SoC design is related to the design of global interconnect. With the scaling of microchip technology, the computation is becoming cheaper than the communication because wires do not scale as transistor due to physical limitation of global wires such as signal integrity (fabrication defects, crosstalk, noise sensitivity) and power consumption. Figure 1.1 from ITRS illustrates the delay gap between wires and transistors for near future technologies. It can be observed that global wires are the most critical in terms of delay, thus, the time spent on global communication can overcome the time spent on local processing. For this reason, there is a need for cost-effective global communication architecture for future SoC design.

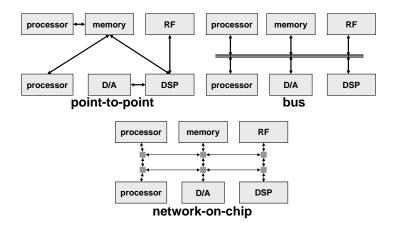

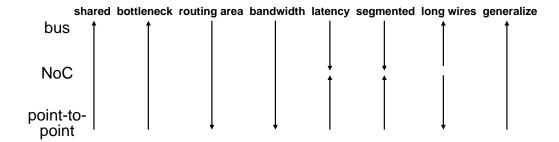

As an answer for the need for a cost-effective global communication for chips, one can observe that the functional interconnects have evolved from point-to-point links, to single and multiple hierarchical buses, and recently to networks-on-chip (NoC) (Figure 1.2). Each of these functional interconnects provides different features as illustrated in Figure 1.3. The increase of number of communicating cores suggests shared and segmented global wires to deal with, respectively, routing area and long wires. On-chip interconnect based on shared global wires are easier to generalize, reducing the design effort, since every core in the system just need to be connected to these global shared wires. However, shared global wires reduce the bandwidth

Figure 1.1: Projected relative delay for local wires, global wires, and logic gates for near future technologies from (ITRS, 2007).

Figure 1.2: Evolution of communication architectures; from dedicated point-to-point links to buses and network-on-chip (adapted from (BJERREGAARD; MAHADE-VAN, 2006)).

and increase the communication *bottleneck*, reducing the parallelism. In addition, segmented global wires increase the communication *latency*, but this problem can be reduced supporting pipeline.

Point-to-point links are optimum in terms of bandwidth, as they are designed for a specific application. But the number of links increases exponentially as the number of cores increases creating routing problems. Moreover, long wires are required in case of distant cores. Long wires degrade the signal, which become more sensitive to noise and crosstalk. Shared global wires alleviate the routing problem, but in case of buses, the problem related to long wires remains. Networks are an approach that share global wires but they are also segmented to avoid long wires. The evolution toward NoCs is a response for the need to reduce the design effort of complex applications (layered design approach, decoupling of communication from computation), need for generalized interconnect solutions, need to deal with Deep SubMicron (DSM) interconnect problems such as power, routing, performance, reliability, and predictability (DALLY; TOWLES, 2001; GUERRIER; GREINER, 2000; BENINI; DE MICHELI, 2002; JANTSCH; TENHUNEN, 2003; BJERREGAARD; MAHADEVAN, 2006). Table 1.1 has been adapted from (GUERRIER; GREINER, 2000; BJERREGAARD; MAHADEVAN, 2006)) to demonstrate some differences of

Figure 1.3: Comparison between communication architectures.

buses and networks.

Finally, although there are many practical issues to be addressed, it is generally agreed that the NoC approach offers several outstanding benefits for future SoCs (BENINI; DE MICHELI, 2002):

- Modularity, thanks to the ability to use basic components such as the Network Interface and the Router (to be presented in Section 2.2);

- Abstraction, a property of the layered approach;

- Flexibility/scalability of the network, as a consequence of packet-based communication;

- Regular and predictable electrical properties to cope with DSM issues;

- Re-use of the communication infrastructure viewed as a platform.

Testing SoC for manufacturing defects is an important challenge since it involves more logic to be tested (ZORIAN; MARINISSEN; DEY, 1998). The test of systems on board is based on the integration of previously tested ICs, and the "system" test comprises only the test of the interconnection among these ICs. However, the test of SoCs require testing all the modules. The increase of the number of transistors in a chip increases the challenges to test the chip. The main reason is the difficulty to access embedded logic through the pins.

NoC solves the problems related to global interconnect, which enables use of newer technology which are more susceptible to manufacturing defects and delay faults. The inclusion of delay test patterns increases the test volume. In addition, since the main motivation of NoC is to give support to design of more complex systems (i.e. more logic), it is expected more test data volume to be transported during test application, increasing the test time and test costs. On one hand, as stated before, the wires are becoming more expensive than logic. The test buses to access the embedded cores will be more expensive. On the other hand, the NoC has access to most cores of the chip and it also supports parallel communication. The reuse of NoC to transport test data, which is the focus of this thesis, seems to be an appealing approach to overcome the costs of test-specific buses. Cota et al. (2003) initially proposed the reuse of a specific NoC architecture for test data transportation. Compared to previous work, our approach is an attempt to generalize and characterize the DfT costs for a given network.

One could ask why it is relevant to study the reuse of NoC instead of point-to-point or buses. The first motivation is to *study communication architecture for future complex SoCs*, which has been demonstrated that both point-to-point and buses can not be applied efficiently. Indeed, there are papers that investigated the reuse of these interconnects for test (COTA et al., 2002; HUANG et al., 2001a; HARROD,

Table 1.1: Comparison between bus and network (adapted from (GUERRIER; GREINER, 2000; BJERREGAARD; MAHADEVAN, 2006)).

|                                          | 1 |   | , ,                               |

|------------------------------------------|---|---|-----------------------------------|

| bus                                      |   |   | network                           |

| Every unit attached adds parasitic       | - | + | Only point-to-point one-way       |

| capacitance, degrading the electrical    |   |   | wires are used, therefore wire    |

| performance.                             |   |   | performance is not degraded.      |

| Bus timing is difficult in a deep        | - | + | Network supports pipelined        |

| submicron process.                       |   |   | communication                     |

| Bus testability is problematic and slow. | - | + | Network can be used to transport  |

|                                          |   |   | test data and network supports    |

|                                          |   |   | multiple parallel communication   |

| Bus arbiter delay grows with the         | - | + | Routing and arbitration logic     |

| number of masters.                       |   |   | are distributed.                  |

| The arbiter is instance-specific.        | - | + | The same arbitration logic        |

|                                          |   |   | is implemented in each router     |

| Bandwidth is limited and shared          | - | + | Aggregated bandwidth scales       |

| by all units attached.                   |   |   | with the network size.            |

| Bus latency is zero once arbiter         | + | - | Internal network contention       |

| has granted control.                     |   |   | increase the latency (1).         |

| The silicon cost of a bus is             | + | - | The network has a significant     |

| near zero.                               |   |   | silicon area (2).                 |

| Any bus is almost directly               | + | - | wrapper and conversion logic      |

| compatible with most available IPs,      |   |   | in both software and hardware     |

| including software running on CPUs.      |   |   | are required (3).                 |

| The concepts are simple and              | + | - | System designers need reeducation |

| well understood.                         |   |   | for new concepts (4).             |

|                                          |   |   |                                   |

1999; BURDASS et al., 2000; HWANG; ABRAHAM, 2001; FEIGE et al., 1998). However, these approaches would not perform well on both test and functional domains in the near future. Moreover, a NoC is easier to *generalize* than point-to-point links, essential issue for any DfT approach; and it supports more *parallelism* and bandwidth than buses, essential to reduce the chip test time.

#### 1.1 Problems to be Solved

We believe that the effective adoption of NoC reuse in actual designs depends on the following items:

• The actual benefits of NoC reuse compared to conventional approaches based on dedicated TAMs:

The benefits and cost related to NoC reuse approaches are not clear enough. The most common claim of authors proposing NoC reuse is that it would save area since no test-specific TAM is required. On one hand, there are some design approaches based on dedicated TAMs that use information of placement of the cores to minimize the TAM wiring length, reporting negligible TAM costs (despite of the more complex design flow) (GOEL; MARINISSEN, 2003b). On the other hand, most papers about NoC reuse are about optimization algorithms under different constraints, but they do not focus on the requirements for the NoC reuse. i.e. which modifications are required in the design in order to reuse the NoC to transport test data? What is the impact of the required DfT for NoC reuse in silicon area and test length compared to dedicated TAMs? If the only benefit of NoC is to save wiring area, how much area are we saving with NoC reuse?

• Simple, general, and application-independent test approach:

Test designers have adopted modular testing approach for the test of complex chips since it is simple. It is mostly based on the well-know scan chains for intra-core access and simple TAMs, which are just wires, for inter-core access. Differentiated core structures, like memories, use BIST approaches. However, the BIST control itself is connected to the chip test control logic by, for example, boundary scan (i.e. more scan-based approaches). Simple approaches usually cost less in area and are easier to automate. In addition, scan can be used to most logic cores, so they are general and independent of design. On the other hand, NoCs are much more complex than conventional dedicated TAM, there is no general NoC design, and the NoC design is totally dependent on the application requirements; so, why reuse NoC for test instead of test-specific TAMs? Is it possible to generalize NoC reuse? Is it possible to simplify the test view of a given NoC?

#### 1.2 Goals

The strategic goal of this thesis is to propose a general<sup>1</sup> approach for the reuse of on-chip networks for test data transportation. To accomplish this strategic goal, the following specific objectives should be fulfilled:

<sup>&</sup>lt;sup>1</sup>The term 'general', unless specified, refers to a test approach that is applicable to most best-effort and mesh-based NoC designs, which was the class of NoC most used along this thesis.

- Make the requirements for NoC reuse explicit;

- Determine the test logic required to enable the reuse of both best-effort (BE) and guaranteed throughput (GT) NoCs;

- Determine the optimization algorithms for the DfT modules;

- Propose a test schedule tool for overall test architecture optimization considering BE NoCs;

- Compare the proposed test architecture with the conventional test architecture based on dedicated TAM to establish the actual advantages and drawbacks of NoC reuse.

#### 1.3 Contribution

The main contribution of this thesis is a general test model for NoC-based SoCs such that this proposed model is compatible with the current test methods. Others contributions are:

- 1. Concise functional NoC definition (Chapter 1);

- 2. Extensive analysis of prior work (Chapter 3);

- 3. General test model for a BE NoC-based chip (Chapter 4), partially published in Amory (2007);

- 4. Detailed design and optimization of DfT required to enable the reuse of both BE and GT NoCs as TAM (Chapters 4 to 7), published in Amory et al. (2005; 2006; 2007; 2007);

- 5. Test planing tool based on the proposed test model to optimize the chip test length (Chapter 8), to be published.

#### 1.4 Outline of the Thesis

This thesis is organized in three parts as presented below.

#### 1.4.1 Background, Definitions, and Models

Chapter 2 presents background related to SoC testing and NoCs. In sequence, the prior work is reviewed in Chapter 3; topics like wrapper design, TAM design, FIFO testing, and recent papers about test of NoC are analyzed. Later, in Chapter 4, we propose a test model that represents the necessary and sufficient information of a BE NoC-based system to implement the DfT and optimization procedures proposed in this thesis.

#### 1.4.2 DfT Design for NoC Reuse

Once the NoC definition is established and the set of required information for test is defined, we detail the design processes required to modify the chip for test. The second part of this thesis, in Chapters 4 to 7, presents the *DfT logic required to use both BE and GT networks to transport test data*.

To use the network for test, some additional logic is required to interface the external tester to the network, to the cores, and to the network building blocks as well. It has been identified, for example, that not only the cores, but also the test pins require a wrapper logic in order to connect to the NoC. Besides, the wrapper requires a different design compared to the conventional modular test approaches because the "TAM" works with well-defined protocols. The proposed wrappers have been designed to abstract the test path as "pipelines" that can pump data at different rates.

#### 1.4.3 Test Optimization

Considering the chip information required for test enumerated in the test model and the required test circuitry, the final step is to integrate it into a test planning tool that optimizes the test architecture in terms of test length and silicon area (Chapters 8 and 9).

## 2 RELATED BACKGROUND

The following sections present basic concepts related to test of SoC, basic concepts of NoC design, and the outline of this thesis.

#### 2.1 Modular Testing

Modular testing (GOEL; MARINISSEN, 2003a), i.e. testing individual SoC modules as stand-alone units, has been used for SoCs. Non-logic modules such as embedded analog and memories require modular testing since they use different test strategies then random digital logic. The ability to use the most appropriate test strategy for every core increases the test quality. Black-boxed cores, such as hard or encrypted cores which no implementation detail is given, require modular testing because they need to be tested with test vectors supplied by the core provider. In addition, modular testing provides an attractive "divide-and-conquer" test development approach that reduces the time to generate the test vectors, and allows for test reuse when a core is used in multiple designs.

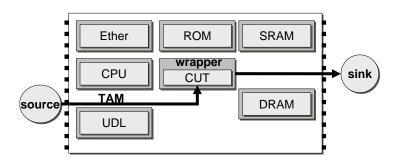

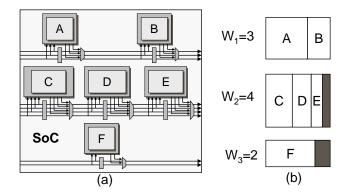

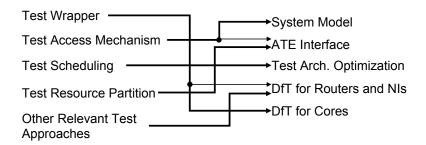

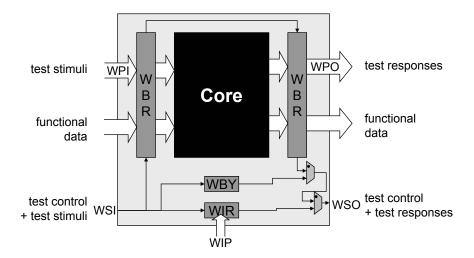

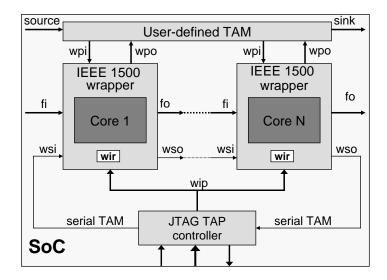

Nevertheless, a core is typically embedded in the SoC and there is no direct access from the SoC pins to the core terminals. Modular testing requires every core to have test access from its terminals to the chip pins, and to be isolated from its surrounding circuitry. Zorian et al. (1998) introduced a general conceptual test architecture (Figure 2.1) for modular testing of SoCs. It consists of three elements per Core-Under-Test (CUT): (i) a test pattern source and sink, which generates and evaluates the test stimuli and responses, respectively (ii) a Test Access Mechanism (TAM), which transports test data from the source to the CUT and from the CUT to the sink, and (iii) a test wrapper for isolation during test mode and to enable switching between the functional access to the test access through the TAM.

Figure 2.1: general conceptual test architecture (from (ZORIAN; MARINISSEN; DEY, 1998)).

Figure 2.2: (a) Example of TestRail architecture and (b) corresponding test schedule (adapted from (GOEL; MARINISSEN, 2003a)).

The test architecture design problem can be defined as (GOEL; MARINISSEN, 2003a): for a given set of cores and a given number of test pins, determine the TAM type, the number of TAMs, the width of each TAM, the assignment of cores to the TAMs, and the wrapper design, such that the chip test length is minimized. Several papers have investigated test architecture designs, such as test bus (VARMA; BHATIA, 1998) and TestRail (MARINISSEN et al., 1998), and how to optimize the test architecture (CHAKRABARTY, 2000; MARINISSEN; GOEL; LOUSBERG, 2000; HUANG et al., 2001b; GOEL; MARINISSEN, 2003a). Figure 2.2 illustrates an example of resulting test architecture and test scheduling (GOEL; MARINISSEN, 2003a).

Two test flows are required to test a core. The *stimuli test flow* transports the test stimuli from the source to the CUT and the *response test flow* transports the test responses from the CUT to the sink. The stimuli and the response test flows may transport different data amounts. For instance, let us assume the test of a core with one input terminal, no internal scan chains, and one hundred output terminals. Each test pattern of this core requires one bit in and one hundred bits out. The *test data volume*, the number of bits required to test a core, considering both stimuli and responses, is given by the core provider, thus, the test data volume is considered invariant.

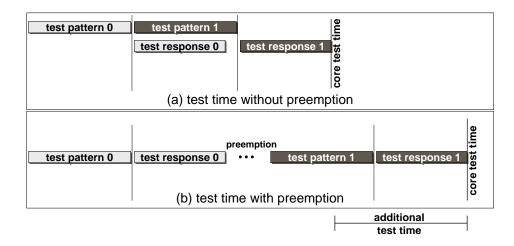

Since the amount of test data is fixed, the core test length<sup>1</sup> depends on how fast the amount of test data can be transported over the TAM. This variable is called test data rate. A recommended test data rate should range from 1 bit/clock cycle to a certain maximum which depends on the core and on the TAM width. The minimal test data rate of 1 bit/clock cycle is recommended, but not mandatory, because it keeps a minimal but constant data flow and it reduces the core test length.

Interruptions on the data flow require mechanisms to halt the test. The usual approaches are the use of clock gating or holdable scan cells. Clock gating halts the clock for a certain period. The drawback is that it requires changing the clock tree, which is generally not recommended for complex systems. The other approach to freeze the test is to implement holdable scan cells, i.e. scan cells that can keep the current value, but this approach requires an extra multiplexer for each scan cell. Holdable scan cells increase the area for DfT. Moreover, it is not feasible for

<sup>&</sup>lt;sup>1</sup>the term test length is used when the unity is clock cycles. Test time is used when we refer to seconds.

Figure 2.3: Core test length for non-preemptive and preemptive test.

hard-core since it is not possible to change the hardware description.

Interruptions in the data flow have an additional drawback in test length. Every time the flow is interrupted, the parallelism between scan-in and scan-out is broken, increasing the core test length. This effect, illustrated in Figure 2.3(a), is referred as test pipeline. Figure 2.3 shows that preemptive test increases the core test length since scan-in is not carried out in parallel with the scan-out.

Another drawback related to interruptions or gaps in the data flow is that most ATEs expect test stimuli and responses as streaming data. ATEs are typically not prepared for more complex interactions with the SoC.

On one hand, assuming a constant test data rate avoids halting the test. On the other hand, the TAM has to guarantee this constant data rate. Dedicated test architectures like the one illustrated in Figure 2.2 naturally guarantee a certain test data rate because the TAM is basically just wires and buffers connecting the test pins to the CUTs. In addition, each core in a TAM is usually tested sequentially to guarantee the exclusive access to the core.

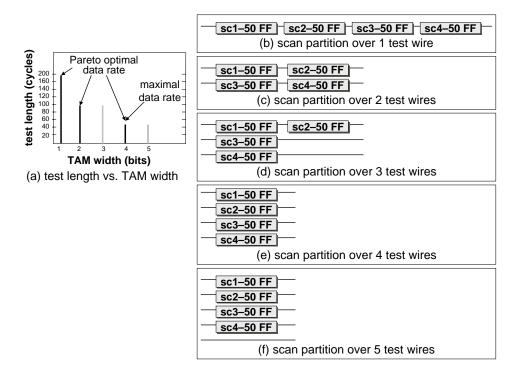

Figure 2.4 illustrates the effect of the assigned test wire on core test length. It also demonstrates two concepts: Pareto optimal test wires (a multi-variable optimization) and the maximal test wire (GOEL; MARINISSEN, 2003a). For example, let us assume a hypothetical hard-core with four internal scan chains, each one with 50 flip-flops. Assigning just one test bit for the test of this core results in a scan length of 200 cycles because the four scan chains are concatenated. As more test wires are assigned, the scan length reduces. However, the reduction has a limit, in this case, when 4 bits/cycle are assigned. Beyond this limit the scan length does not reduce. Moreover, the scan length reduction plot does not have a perfect stair-case behavior. Some situations, like the one with 3 bits/clock cycle, may not result in a reduction in the scan length compared to, for example, 2 bits/clock cycle. This effect occurs due to the sizes of the internal scan chains.

Only scan configurations that strictly reduce the scan length are allowed. That is, if two scan configurations lead to the same scan length for a core, the one with smaller number of test wires is chosen. In our example, 4 is a Pareto optimal test wire because 1, 2, and 3 lead to a higher test length than 4. In contrast, 5 is not Pareto optimal because 4 leads to the same test length than 5. Maximal test wire is the maximal Pareto optimal test wire. The maximal bandwidth for the example in

Figure 2.4: Core test length vs. bandwidth.

Figure 2.4 is 4 bits/cycle. Defining the test bandwidth to the maximum would minimize the core test length. Nevertheless, it would require expensive communication resources from the chip. Moreover, a SoC typically has multiple cores. Assigning the maximal bandwidth for each core is unfeasible since the number of test pins is usually small. One of the goals of a test scheduling tool is to find this trade-off such that the chip test time is minimized. A cost effective distribution of test bandwidth to the cores to minimize the test length is a common subject of research (CHAKRABARTY, 2000; HUANG et al., 2001b; IYENGAR; CHAKRABARTY; MARINISSEN, 2002a; GOEL; MARINISSEN, 2003a).

# 2.2 Networks-on-Chip

This section presents basic concepts regarding NoCs. It is not intended to be a extended review of network design; for such, titles like Duato et al. (2003), McCabe (2003), Jantsch and Tenhunen (2003), and Bjerregaard and Mahadevan (2006) can be used. The emphasis is given on the basic concepts, the most important building blocks (architecture and hardware implementation), their role (capabilities that can be useful for test), and their interaction (protocols, timing, and terminal-to-terminal binding).

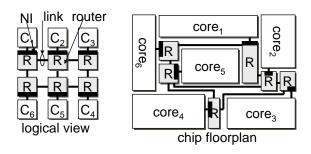

A given application in the context of chips consists of nodes, which are typically processing units, memory, standard I/O, or combination of them, that need to communicate with each other to complete a certain task. Different kinds of communication media can be employed; each of them with different costs and performance. NoCs are a recent proposal which are more cost effective for very complex designs. In a NoC-based chip, cores communicate with each other via a network which consists of network interfaces (NI), routers, and links (two channels in opposite directions) (RADULESCU et al., 2005). Figure 2.5 illustrates a floorplan and a common logical

Figure 2.5: A simple NoC instance.

Figure 2.6: A typical router architecture (DUATO; YALAMANCHILI; NI, 2003). LC denotes link controller.

view of a possible NoC instance.

A router, which can also be called switch in the literature, is the main building block of a network; it handles the message communication among the nodes. A router has a number of input and output ports (i.e. the router degree), where one of these ports may connect to a node and the remaining connect to neighbors or adjacent routers. The way that adjacent routers are connected define the topology and can be modeled by a graph G(N, C), where the vertices of the graph N represent the set of routers and the edges of the graph C represent the set of channels. Many topologies have been proposed to balance performance and cost parameters.

Nodes communicate with each other sending *messages*, which for performance reasons may be divided into *packets* before the transmission. Packets are the unit of communication that contains the packet *header* which carries additional information such as the destination address. A *routing algorithm* determines the intermediate routers transversed (the path) by the packets to reach the destination. The routing algorithm determines the output port of a packet.

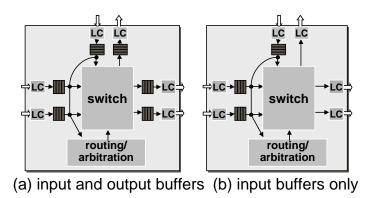

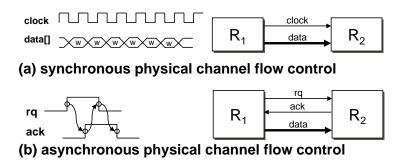

A typical router architecture is illustrated in Figure 2.6. Inside a router, when a packet header arrives in an input channel, the *switching* mechanism determines how and when the network resources are allocated for the message transfer (DUATO; YALAMANCHILI; NI, 2003). The typical resources are channels and *buffers*. The buffers are used to store data temporally until the output channel is chosen or it is freed. *Flow control* mechanism establishes the communication between two adjacent routers, controlling the data flow as the buffer space is free. Examples of channel flow control are illustrated in Figure 2.7.

The architecture of a router, illustrated in Figure 2.6, typically consists of the following components (DUATO; YALAMANCHILI; NI, 2003):

Figure 2.7: Examples of physical channel flow control (adapted from (DUATO; YALAMANCHILI; NI, 2003)). (a) synchronous and (b) asynchronous.

- Buffers: They are First-In First-Out (FIFO) buffers used to store messages in transit. They can be implemented in the input ports (Figure 2.6(b)), output ports, or both (Figure 2.6(a)).

- Switch: This component is responsible for connecting the input ports to the output ports.

- Routing and Arbitration: This component implements the routing algorithm and selects the output port for an incoming message. This component also provides arbitration in case there are multiple requests for the same output port.

- Link Controller(LC): This component implements the channel flow control between adjacent routers.

The switching mechanism, flow control mechanism, and buffer management have direct impact on the network performance (DUATO; YALAMANCHILI; NI, 2003; MCCABE, 2003). Let us define some performance metrics. *Throughput* is the rate (bits/s) at which a network device sends or receives data. *Bandwidth* is the maximum theoretical throughput. It indicates the maximum amount of data that can pass from one point to another in a unit of time. Throughput is more like a measure of the usage of a resource and bandwidth is the measure of the resource itself. *Latency*, or delay, is the time elapsed from the beginning of data transmission until the time data is received at destination. *Jitter* is a measure of delay variation over time.

Routers with different designs and architecture require a different analytical performance model. For example, Equations 2.1 and 2.2 model the no-load packet latency (latency in the absence of any traffic) for the router architectures depicted in Figure 2.6(a) and (b), respectively (DUATO; YALAMANCHILI; NI, 2003).

The packet to be transferred has a size of L bits. The physical data channel width has W bits. Assuming a one word header, the total packet size is L/W bits. The router does the routing decision in  $t_r$  seconds; the physical channel runs at B Hz. Thus, the physical channel bandwidth is  $B \times W$  bits per second. Assuming that the channel wires can complete a transmission in one clock cycle. Therefore, the propagation delay is  $t_w = \frac{1}{B}$ . Once the routing path has been set up, the switching delay is denoted by  $t_s$ . Thus, a word can be transferred from the input channel to the output channel in  $t_s$  seconds. The distance between the source and destination is assumed to be D hops. Figure 2.8 illustrates these variables. The expression  $D(t_r + t_s + t_w)$  represents the network latency, while the rest of the equation represents the time to transfer a given amount of data L over W wires

Figure 2.8: Latency from the source to the destination (adapted from (DUATO; YALAMANCHILI; NI, 2003)).

in a pipelined manner. With input and output buffers, the pipeline cycle time is determined by the maximum of the switch delay and the wire delay  $\max(t_s, t_w)$ . For input-only or output-only, the cycle time is the sum of  $t_s + t_w$ .

$$t_{wormhole1} = D(t_r + t_s + t_w) + \max(t_s, t_w) \times \left\lceil \frac{L}{W} \right\rceil$$

(2.1)

$$t_{wormhole2} = D(t_r + t_s + t_w) + (t_s + t_w) \times \left\lceil \frac{L}{W} \right\rceil$$

(2.2)

These equations exemplify how router design decisions impact the network performance. This level of design details may be considered complex for our goal of designing general network models since there is a huge number of possible design variations, thus, huge number of corresponding analytical models.

Up to now, just the most basic communication 'services' have been described. However, complex applications may require more complex services. For examples, some applications may require additional reliability, thus, services as error detection, error correction, and packet retransmission may be implemented. Choosing a proper boundary and location of the required services are perhaps one of the first design steps. The end-to-end design principle (SALTZER; REED; CLARK, 1984), applied for distributed systems, says that it is usually better to place application-dependent functions (or services) closer to the application that uses the function. In the case of core-based chip design the 'application' is a core and the 'function' is, for example, a mechanism to give support to reliable data transfer. For this reason, only the basic communication services are implemented in the routers (in side the network) and the optional and application-dependent services are implemented in the boundaries of the network with the cores, commonly called Network Interface (NI). Note that the application-dependent services could also be implemented in the cores, but it would impair the core reusability to other systems.

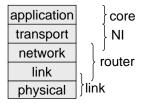

The services implemented in the NIs are usually described in a layered manner, with the advantage of abstracting the most basic services which are closer to the implementation details (MCCABE, 2003; RADULESCU et al., 2005; KEUTZER et al., 2000). The global on-chip communication can be decomposed into five layers (TANENBAUM, 1996). The protocol stack enables different services and allows Quality of Service (QoS) mechanisms, providing to the programmer an abstraction of the communication framework. Layers interact through well-defined interfaces and they hide the low-level physical DSM issues. Figure 2.9 correlates the most important protocol layers and where they are implemented in the NoC. The Physical layer refers to the electric details of wires, the circuits and techniques to drive

Figure 2.9: Protocol layers and the main building blocks of a NoC-based design.

information (drivers, repeaters, and layout). The Data Link level ensures a reliable transfer and deals with medium access (sharing/contention). The Network level deals with issues related to the topology and routing scheme. Finally, the Transport layer manages the end-to-end services and the packet segmentation/re-assembly. QoS, which helps to decouple communication from the computation, is also implemented at the transport layer. The Application is implemented in the set of cores of the chip. For the core point-of-view the services should be transparent (abstracted). For example, a core sends and receives raw data (without packetization) without knowing that there is a NI that provides reliable data transfer.

The communication services can be implemented either in software or in hardware, however, in the context of chips, which has tighter latency constraints, it is preferable to implement these services in hardware. In addition, recall that not all nodes in a NoC are programmable, thus, if additional services are required, they have to be implemented in hardware. Therefore, just an indispensable set of services is implemented since there is also area constraint. The set of most used network services are (MCCABE, 2003): packetization, responsible for inserting and removing the header, the sequence number, the parity, the CRC, or the check sum information into the packet; buffering used to overlap communication an computation, which requires an end-to-end flow control mechanism to control the buffer usage; packet ordering in case adaptative routing is supported, which also requires sequence number in the packet header; reliable data delivery ensures that the destination receives the correct information. It may include error detection, error correction, or packet retransmission mechanisms; soft or hard performance quarantees for latency, jitter, or bandwidth, which may require mechanisms for resource reservation; collective communication like the support of one-to-many and one-to-all communication patterns rather than just one-to-one.

Another relevant consideration is how the cores are connected to the network. It has been demonstrated that the cores are connected to the router network through a NI, however, NIs need a standard interface to do the terminal-to-terminal connection of the cores to the NoC. Thus, the NoCs assume that both cores and NIs are connected via a memory-mapped on-chip port like OCP (OCP-IP, 2003), AXI (ARM, 2004a), VCI (ALLIANCE, 2000), or DTL (PHILIPS SEMICONDUCTORS, 2002). The advantage is that no matter the NI design, the connection of the cores and the network is facilitated, reducing the design effort. Such practice has been used for other interconnect, like buses. Indeed, these memory-mapped types of ports are inherited from buses. They are used for NoCs just to keep the compatibility with existing cores, since they increase the packet latency when used for NoCs (OST et al., 2005). In the near future new communication approaches specific for networks (like message passing) may come up for NoCs to reduce the packet latency.

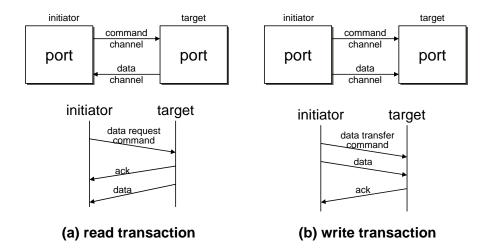

Figure 2.10: Initiator and target ports; read and write transactions.

A port may be classified as *initiator or target* (sometimes also called master or slave), and as *read*, write, or read/write port. An initiator port starts transactions which are sent to a target port; a target port just receives and executes transactions. A transaction can be split into read or write commands. A read command (Figure 2.10(a)) sends a request command from the initiator to the target port; the target port acknowledges it and sends the requested data. A write command (Figure 2.10(b)) sends data from the initiator to the target; the target consumes the received data and acknowledges it. A port is usually configurable, thus, it may not necessarily support both read and write commands. For example, some valid port usages are: an initiator read port starts read commands; an initiator write port starts write commands; a target read/write port answers both read and write commands.

Figure 2.11 illustrates an OCP-like port and its protocol. The main principles can be applied to other protocols. Event 1 in Figure 2.11 represents the request of a write command to send two words, which is accepted in the next clock cycle, during the event 2. The first word is sent during the event 3, when the data valid is high. In event 4 the target does not accept the second word, but it is accepted in event 5. The read command works in a similar way.

One may have realized that several concepts about router design were not presented on this Section. Recall that the main goal of this thesis is to conceive a general test approach for NoC based on network reuse to transport test data. If all kind of design decision is required to a model, the generality is compromised. Thus, just the required notions were presented.

#### 2.2.1 Functional NoC Model

This section presents the informal functional NoC model and its assumptions. This is the functional NoC model used in this thesis. Figure 2.12 demonstrates one valid instance of the proposed functional model:

- Routers are connected to other routers and to zero or one NI via links;

- A *link* consists of two pairs of router ports and two channels such that data flows in both directions in the *channels* (see Section 2.2.1.1);

- Router ports implement the channel protocol, like the one illustrated in Fig-

Figure 2.11: Protocol of an OCP-like port.

ure 2.7, and all router ports have the same configuration, i.e. the same width, bandwidth, and protocol (see Section 2.2.1.1);

- Core ports implement an on-chip protocol such as OCP. Each core port is configured individually and the data flow can be unidirectional or bidirectional;

- A NI has one or more core ports and only one router port;

- A *core* connected to the NoC has two or more core ports. Core ports are not required for cores not connected to the NoC;

- A NI connects to one or more cores via core ports;

- A core connects to zero or more NIs via core ports;

- Pins are connected only to cores (see Section 2.2.1.2);

- Only synchronous systems are considered (see Section 2.2.1.3);

- The routers must be organized in a mesh topology.

The model requires NIs to do the interface among the cores and the routers. The minimum requirement for NI is packetization (i.e. conversion from a core protocol like OCP to a channel protocol like handshake) to abstract the packet format from the cores. Thus, the cores manipulate raw data through the on-chip ports. Core are typically memory mapped, thus, the address information sent from the core to the NI via the port is used to select the destination. In this way, the cores do not realize the existence of a NoC; they just have to obey the on-chip protocol.

Note that there is no information related to the implementation of the modules, except by packetization for NIs and routing algorithm. For instance, we do not require multicast service, or any other kind of network service. For this reason this functional model is used as a stepping stone for the proposed general test model presented in Chapter 4.

## 2.2.1.1 Link and Router Configuration

There might be NoCs with unidirectional links, like in ring topologies. In additional, it is also possible to have NoCs whose channel widths are different. For instance, a certain channel might require higher bandwidth, so wider channel width might be used. Likewise, there might be routers whose ports have different width or even different channel protocols. We believe that these considerations might be implemented, however, they are unusual. Thus, we assume, for sake of simplicity,

Figure 2.12: A more complex NoC instance.