# Pontifícia Universidade Católica do Rio Grande do Sul Faculdade de Engenharia – Faculdade de Informática Curso de Engenharia de Computação

# PrimeSec: Sistema de Detecção de Intrusão em Redes de Computadores sobre uma Plataforma Multiprocessada

Volume Final de Trabalho de Conclusão

#### Autores

Guilherme Montez Guindani Hugo Artur Weber Schmitt

#### Orientador

Prof. Fernando Gehm Moraes

Porto Alegre, 30 de novembro de 2006.

# Índice

| 1 | Intro        | odução                                                                         | 1  |

|---|--------------|--------------------------------------------------------------------------------|----|

|   | 1.1          | Motivação                                                                      | 1  |

|   | 1.2          | Objetivos                                                                      | 2  |

|   | 1.3          | Estrutura deste Documento                                                      | 2  |

| 2 | Refe         | erencial Teórico                                                               |    |

|   | 2.1          | O Modelo OSI-RM                                                                |    |

|   | 2.2          | A Definição dos Pacotes Ethernet                                               | 4  |

|   | 2.3          | A Definição dos Datagramas IP                                                  | 6  |

|   | 2.4          | A Definição dos Segmentos TCP                                                  |    |

|   | 2.5          | A Definição dos Datagramas UDP                                                 |    |

|   | 2.6          | A Definição das Mensagens ICMP                                                 |    |

| 3 |              | OS – Sistemas de Detecção de Intrusão em Redes                                 |    |

|   | 3.1          | Snort – Descrição de operação                                                  |    |

|   | 3.2          | Snort – O formato das regras                                                   |    |

| 4 | Imp          | lementação de NIDS em Hardware                                                 |    |

|   | 4.1          | SPP-NIDS – Um NIDS em Hardware                                                 |    |

|   | 4.1.         | 1                                                                              |    |

|   | 4.1.         | C 1 1,                                                                         |    |

|   | 4.1          | 1 1                                                                            |    |

|   | 4.1.4        | 1                                                                              |    |

|   | 4.1.:        |                                                                                |    |

|   | 4.1.0        | 11                                                                             |    |

|   | 4.1.         |                                                                                |    |

|   | 4.1.3        | 1                                                                              |    |

| _ | 4.2          | FORCE10 P-Series                                                               |    |

| 5 |              | neSec - Um NIDS em Hardware Multiprocessado                                    | 29 |

|   | 5.1          | Visão geral da arquitetura do PrimeSec                                         |    |

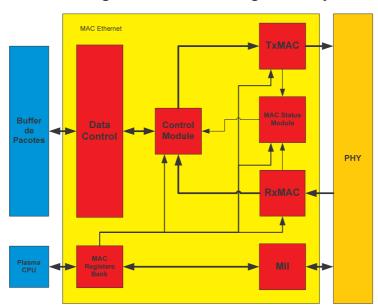

|   | 5.2          | O módulo MAC Ethernet 10/100 Mbps                                              |    |

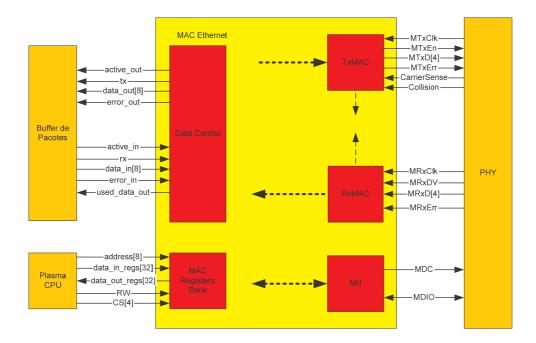

|   | 5.2.<br>5.2. |                                                                                |    |

|   | 5.2.         | Descrição das interfaces externas do módulo MAC Ethernet  O Processador Plasma |    |

|   | 5.4          | O cluster GIOIA                                                                |    |

|   | 5.5          | Visão geral das interfaces internas do PrimeSec                                |    |

|   | 5.5.         | =                                                                              |    |

|   | 5.5.         |                                                                                |    |

|   | 5.5.         | , 1                                                                            |    |

|   | 5.5.         | 1                                                                              |    |

|   | 5.5.         |                                                                                |    |

|   | 5.5.0        |                                                                                |    |

| 6 |              | atégia de Validação Funcional do PrimeSec                                      |    |

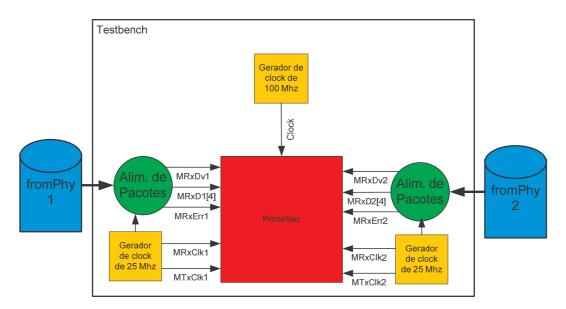

| Ü | 6.1          | Estrutura do testbench utilizada                                               |    |

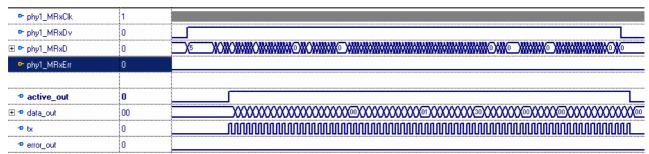

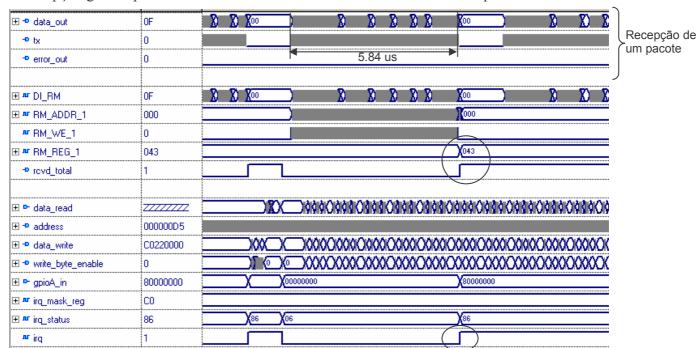

|   | 6.2          | Validação da interface de recepção de pacotes da rede sem segurança            |    |

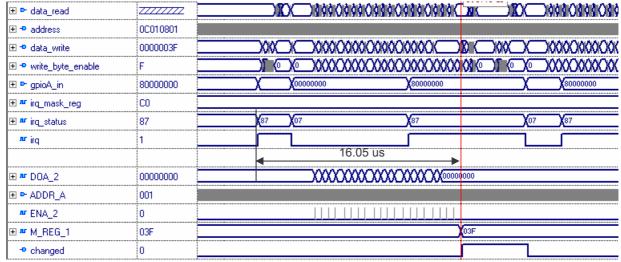

|   | 6.3          | Validação da interface de verificação dos pacotes                              |    |

|   | 6.4          | Validação da interface de transmissão de pacotes à rede segura                 |    |

|   | 6.5          | Validação da interface de recepção de pacotes da rede segura                   |    |

|   | 6.6          | Validação da interface de configuração e monitoração do sistema                |    |

|   | 6.7          | Validação da interface de transmissão de pacotes a rede sem segurança          |    |

| 7 |              | clusões e Trabalhos Futuros                                                    |    |

| Ω |              | erências Rihliográficas                                                        |    |

# Índice de Figuras

| Figura 1 - O OSI-RM e um exemplo típico de sistema operacional de rede [TOR01]                  | 4   |

|-------------------------------------------------------------------------------------------------|-----|

| Figura 2 - Quadro Ethernet (IEEE 802.3 básico) e Ethernet II (DIX) [TOR01].                     |     |

| Figura 3 - Relação dos protocolos da pilha TCP/IP com o modelo OSI [TOR01]                      |     |

| Figura 4 - Estrutura do cabeçalho de um datagrama IP.                                           |     |

| Figura 5 - Encapsulamento dos dados e dos diversos protocolos na pilha TCP/IP [TOR01]           |     |

| Figura 6 - Um exemplo que ilustra a rede na visão do protocolo TCP                              |     |

| Figura 7 - O handshake de três vias usado no fechamento de uma conexão                          |     |

| Figura 8 - Estrutura do cabeçalho de um segmento TCP                                            |     |

| Figura 9 - Formato do cabeçalho de um datagrama UDP                                             |     |

| Figura 10 - Formato do cabeçalho de uma mensagem ICMP                                           |     |

| Figura 11 - Árvore de diretórios de instalação do Snort e trecho do diretório das regras        |     |

| Figura 12 - Arquitetura simples com NIDS e roteador opcional                                    |     |

| Figura 13 - Rede com DMZ Firewall e Snort.                                                      |     |

| Figura 14 – Diagrama de blocos da arquitetura do SPP-NIDS                                       |     |

| Figura 15 – Estrutura geral do protótipo da plataforma SPP-NIDS.                                |     |

| Figura 16 - Organização das memórias DPRAMs utilizadas pelas pico-CPUs                          |     |

| Figura 17 - Conjunto de sinais de entrada/saída de dados e controle de uma pico-CPU             |     |

| Figura 18 – Estrutura interna do bloco de dados de uma pico-CPU.                                |     |

| Figura 19 – Interface interna do cluster e a interface com a CPU de controle IDS.               |     |

| Figura 20 – Interfaces e estrutura parcial do wrapper do cluster.                               |     |

| Figura 21 - Modelo de filtros usado na plataforma P-Series.                                     |     |

| Figura 22 - Firewall P-Series, da empresa Force10.                                              |     |

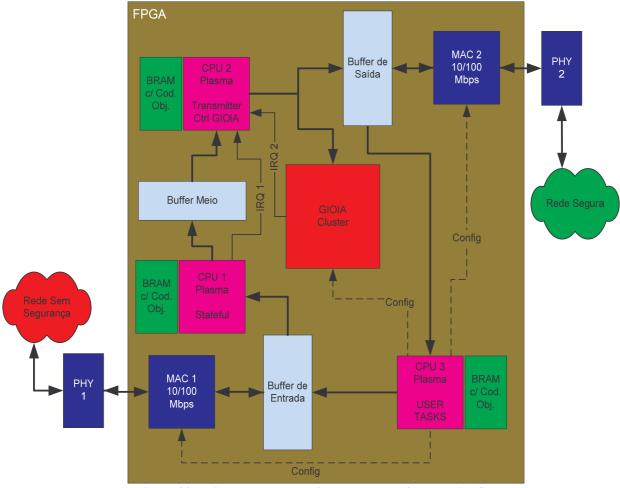

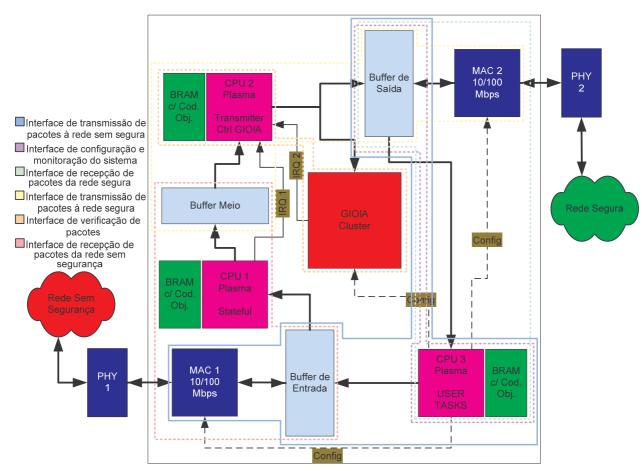

| Figura 23 – Visão geral da arquitetura da plataforma PrimeSec.                                  |     |

| Figura 24 - Visão geral da arquitetura do MAC Ethernet e seu contexto de uso                    |     |

| Figura 25 – Interface com a camada física Ethernet PHY e a interface com os módulos internos    |     |

| sistema                                                                                         |     |

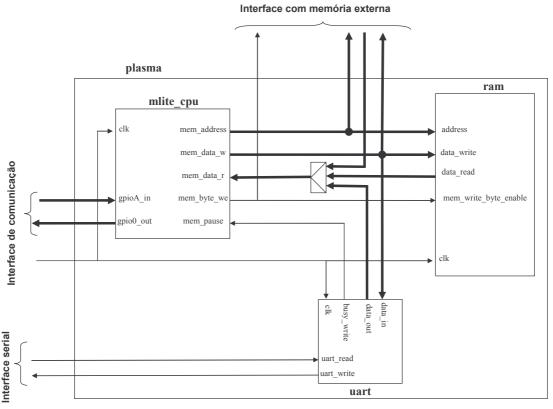

| Figura 26 - Visão da arquitetura do processador Plasma e suas interfaces externas.              |     |

| Figura 27 - Principais interfaces do sistema PrimeSec.                                          |     |

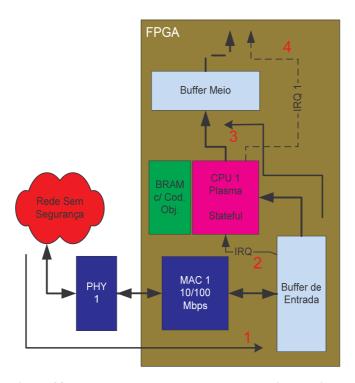

| Figura 28 - Fluxo de dados de um pacote recebido no sistema.                                    |     |

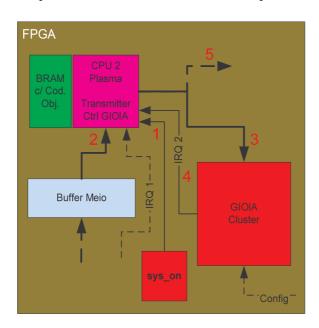

| Figura 29 – Fluxo de dados de um pacote na interface de verificação de pacotes.                 |     |

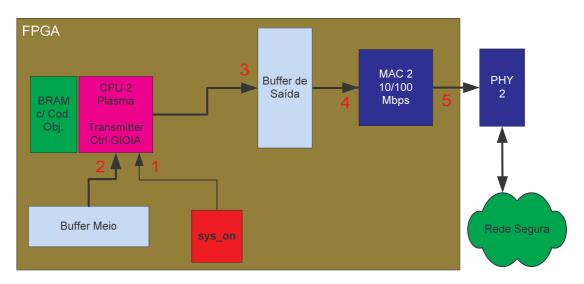

| Figura 30 - Fluxo de dados de um pacote na interface de transmissão de pacotes à rede segura    |     |

| Figura 31 - Fluxo de dados de um pacote na interface pacotes da rede segura.                    |     |

| Figura 32 - Fluxo de dados de um pacote na interface configuração e monitoração do sistema      |     |

| Figura 33 - Estrutura do cabeçalho de um pacote de configuração.                                |     |

| Figura 34 - Fluxo de dados de um pacote na interface transmissão de pacotes à rede sem segura:  |     |

|                                                                                                 |     |

| Figura 35 - Estrutura do testbench utilizado nas simulações do sistema PrimeSec                 |     |

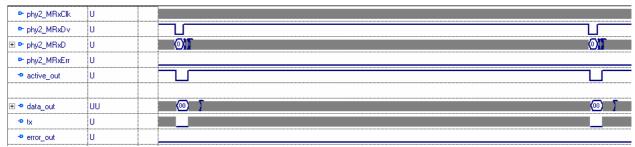

| Figura 36 - Recepção de um pacote no MAC Ethernet 1.                                            |     |

| Figura 37 - Operação de repasse do pacote do Buffer de Entrada ao Buffer Meio.                  |     |

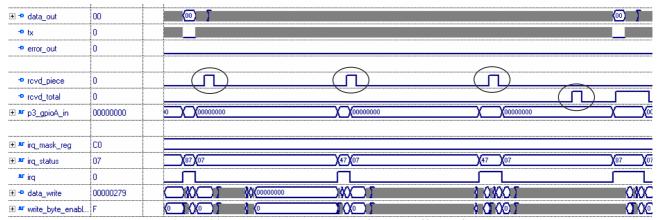

| Figura 38 - Pacote sendo escrito no Buffer Meio e a interrupção gerada ao Plasma 2              |     |

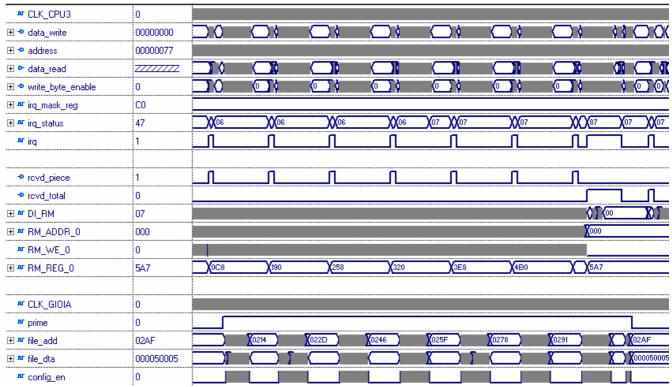

| Figura 39 - Repasse dos bytes do conteúdo do pacote ao cluster.                                 |     |

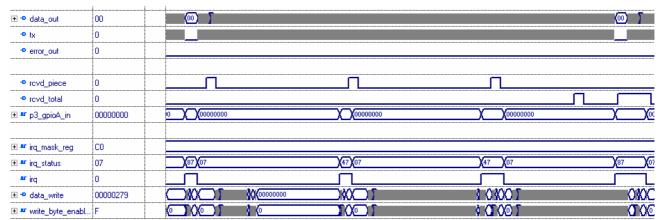

| Figura 40 - Sinalização da detecção de uma regra no pacote em comparação via interrupção        |     |

| Figura 41 - Operação de repasse do pacote ao Buffer de Saída para transmissão                   |     |

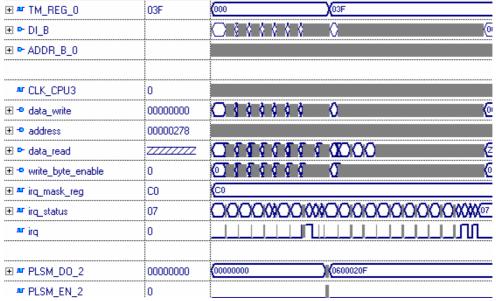

| Figura 42 - Transmissão de um pacote do MAC Ethernet 2 à rede segura                            |     |

| Figura 43 - Recepção de um pacote no MAC Ethernet 2.                                            |     |

| Figura 44 - Interrupção do Plasma 3 pelo Buffer de Saída.                                       |     |

| Figura 45 - Configuração das regras do cluster através da interface de configuração e monitoraç |     |

| do sistemado cistema                                                                            |     |

| Figura 46 – Troca de memória realizada pelo Plasma 3.                                           |     |

| Figura 47 - Interrupção do Plasma 3 pelo Buffer de Saída                                        |     |

| . 15010 1/ 1110110700 00 1 1001110 2 POID DULLOL UD DULUU                                       | 🗆 / |

#### Índice de Tabelas

| Tabela 1 – Número de regras | por protocolo no Snort v.2.11                  | 24 |

|-----------------------------|------------------------------------------------|----|

|                             | 2, um subconjunto de instruções do MIPS 2000 [ |    |

#### Lista de abreviaturas

ADCCP Advanced Data Communication Control Procedures

ANSI American National Standards Institute

CI Circuito Integrado

**DDCMP** Digital Data Communications Message Protocol

**DEC** Digital Equipment Corporation

**DPRAM** Dual Port Random Access Memory

FCS Frame Check Sequence

**FPGA** Field-Programmable Gate Array

FSM Finite State Machine

FTP File Transfer Protocol

HDLC High-Level Data Link Control

ICMP Internet Control Message Protocol

IDS Intrusion Detection System

IEEE Institute of Electrical and Electronic Engineers

IP Internet Protocol

ISO International Standards Organization

LAN Local Area Network

NIDS Network Intrusion Detection System

OSI Open Systems Interconnect

OSI-RM Open Systems Interconnect Reference Model

RAM Random Access Memory

**SDLC** Synchronous Data Link Control

SOC System-On-a-Chip

SPP-NIDS Sea of Processors Platform for Network Intrusion Detection System

TCP Transmission Control Protocol

**UDP** User Datagram Protocol

VHDL VHSIC Hardware Description Language

WAN Wide Area Network

WWW World Wide Web

### 1 Introdução

O constante crescimento das redes de computadores e sua utilização são acompanhados por um aumento das ameaças à segurança, o que vem a exigir um volume cada vez maior de processamento de dados em segurança de redes.

O maior desempenho dos processadores e o aumento da capacidade das memórias proporcionam incrementos na capacidade de processamento disponível para aplicação em segurança de rede. No entanto, existe um ponto a partir do qual a quantidade de recursos investida em hardware adicional não resultará em um aumento proporcional no desempenho dos sistemas [DES03]. Há de ser considerado que a evolução tecnológica favorece também os "intrusos", tanto mais quanto se coloca à disposição ferramentas sofisticadas de ataque disponíveis na internet [BAS04][ALL03].

Os ganhos necessários na área de segurança de redes, já demonstrados na evolução de técnicas e algoritmos, devem vir do trabalho dos desenvolvedores de *Intrusion Detection Systems* (IDS). Este foi o caso da evolução do *Snort* [CAS03], em que o desempenho do sistema aumentou várias vezes até a versão atual, devido à aplicação de algoritmos mais eficientes.

A maioria dos sistemas de computação utilizados atualmente são sistemas mono processados com um único fluxo de execução seqüencial, o que os limita em desempenho. Uma alternativa a esses sistemas são máquinas paralelas. Entretanto, estas máquinas têm um custo muito mais elevado, em razão da especialização necessária tanto da eletrônica quanto do software empregado. Sistemas operacionais com capacidade de processamento paralelo, linguagens de programação e algoritmos paralelos são específicos por aplicação e exigem práticas diferenciadas em sua produção, aplicação e manutenção e são de baixo desempenho se desenvolvidos para uso geral.

Uma solução para equacionar custo e desempenho é oferecida quando temos co-processadores de uso específico [HAR97][HAU97], em que as unidades especializadas de processamento paralelo integram-se aos sistemas tradicionais com vantagem no custo global do sistema.

A tecnologia de circuitos integrados (CIs) de lógica reconfigurável, como por exemplo FPGAs, permite liberdade na concepção e prototipação de arquiteturas inovadoras. Estes componentes, baseados em um arranjo bidimensional que repete uma mesma célula básica de lógica configurável, possuem um paralelismo nativo. Além deste arranjo básico, outras estruturas mais complexas como blocos de memória ou mesmo processadores são integrados ao componente, aumentando consideravelmente seu poder de computação. Componentes fabricados com esta tecnologia, e com grande densidade de elementos construtivos, tornaram possível a implementação em FPGAs de sistemas computacionais completos em um único CI, conhecidos por SoCs (*Systemon-a-Chip*) [BER01][GUP97].

#### 1.1 Motivação

A necessidade de assegurar o funcionamento de sistemas de computação tem exigido esforços crescentes no sentido de evitar o que se convencionou chamar de intrusão, ou seja, o uso não autorizado ou o uso malicioso de um sistema de computação.

Isto levou à criação de sistemas de detecção de intrusão ou IDS (Intrusion Detection System).

No contexto das redes de computadores, foram criados os NIDS (Network Intrusion Detection System), IDSs especializados na vigilância sobre o tráfego de redes, como é o caso do programa Snort [CAS03][NOR03][NOR03a], aplicação de fonte aberto amplamente utilizada em todo mundo com esta finalidade.

O desenvolvimento de arquiteturas paralelas, integradas em um único circuito integrado abre novas perspectivas relacionadas ao desempenho e a segurança no tratamento de intrusões. Estas arquiteturas ainda são raras no mercado. Um exemplo é a plataforma P-Series da empresa Force10 [FOR06].

#### 1.2 Objetivos

Este trabalho estende o trabalho de mestrado de Luís Carlos Mieres Caruso [CAR05a], o qual propôs uma arquitetura paralela e implementou um primeiro protótipo deste, que é voltada para detecção das regras do Snort. O presente trabalho completa esta arquitetura, integrando-a a interfaces de rede e processadores.

O objetivo deste trabalho é aplicar os conhecimentos adquiridos durante o curso, desenvolvendo uma estrutura de suporte a um co-processador de detecção de padrões. Fazendo isto, tem-se um protótipo de um sistema de NIDS em hardware, denominado Primesec. O PrimeSec utilizará este co-processador para o processamento de padrões, analisando o tráfego entre redes de computadores. Este trabalho visa tornar o conjunto desenvolvido em um pré-produto, ou seja, operacional ao ponto de ser possível realizar testes do protótipo em campo.

#### 1.3 Estrutura deste Documento

O presente documento é organizado como segue. O Capítulo 2 apresenta conceitos de redes, protocolos e pacotes, necessários para a compreensão do presente trabalho. O Capítulo 3 conceitua o que são os NIDS (sistemas de detecção de intrusão em redes), apresentando o Snort, um NIDS em software. O Capítulo 4 apresenta duas implementações de NIDS em hardware: (i) o SPP-NIDS, utilizado como base para o desenvolvimento do presente Trabalho de Conclusão; (ii) um exemplo de arquitetura comercial com características similares à arquitetura proposta neste trabalho. O Capítulo 5 apresenta a principal contribuição do TC: o detalhamento da arquitetura e da implementação do sistema PrimeSec. O Capítulo 6 apresentação a validação da arquitetura PrimeSec. O Capítulo 7 apresenta as conclusões do trabalho e sugere futuros temas de pesquisa em arquiteturas para detecção de intrusão em redes.

#### 2 Referencial Teórico

Neste Capítulo apresentam-se os conceitos básicos de redes relacionados ao tema do presente Trabalho de Conclusão: a definição do modelo OSI-RM, a definição de pacotes Ethernet, IP, TCP, UDP e ICMP.

#### 2.1 O Modelo OSI-RM

O Modelo de Referência para Interconexão de Sistemas Abertos (em inglês, *Open Systems Interconnection Reference Model* ou OSI-RM), proposto pela *International Standards Organization* (ISO), permite a estratificação, o projeto e a implementação dos protocolos padronizados em redes de comunicação. O OSI-RM divide o tratamento de informações de rede em sete níveis de abstração. Estes níveis estão numerados e definidos a seguir:

- **Nível 1 (Físico)**: define o meio de transmissão, suas características elétricas e mecânicas. Exemplos de normas aplicadas neste nível são: RS-232, RS-422A, RS-485 da EIA (*Electronic Industries Association*), etc;

- Nível 2 (Enlace de Dados): estabelece, mantém e permite acesso ao meio físico, empacota mensagens para transmissão e verifica a integridade das mensagens recebidas. Exemplo de normas e padrões aplicados neste nível são: HDLC(ISO), ADCCP(ANSI), DDCMP(DEC), SDLC e BSC (IBM);

- **Nível 3 (Rede)**: controla o encaminhamento das mensagens, gerenciando o seu fluxo dentro e entre redes. Exemplos de normas aplicadas a este nível são: X.20, X.21, X.25 da CCITT (*International Consulting Committee on Telephone and Telegraph*);

- **Nível 4 (Transporte)**: cria e mantém a conexão entre estações, permitindo a conexão lógica segura entre estações;

- **Nível 5 (Sessão)**: estabelece e controla as sessões (mensagens estruturadas) entre duas estações da rede.

- **Nível 6 (Apresentação)**: proporciona uma representação e formato geral de informação trocada entre duas estações da rede. Um exemplo neste nível é a codificação MIME.

- **Nível 7 (Aplicação)**: define regras de sintaxe, semântica e gramáticas para troca de informações no nível de transporte de arquivos, acesso a bases de dados e uso compartilhado de recursos entre duas estações da rede.

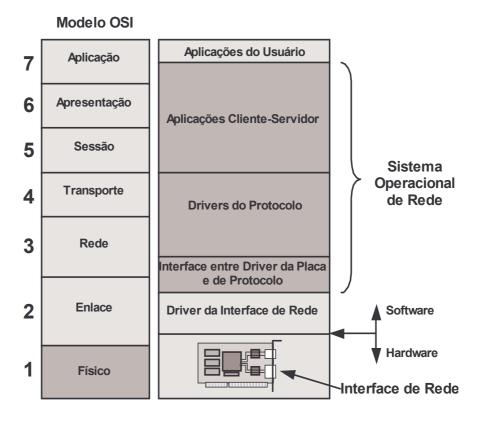

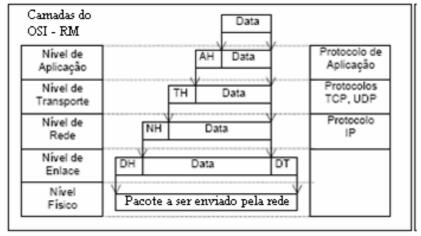

A hierarquia proposta pelo OSI-RM é apresentada no lado esquerdo da Figura 1. Na direita da figura, comparativamente, observa-se uma equivalência com um sistema operacional de rede típico que implementa cada nível do modelo OSI-RM [TOR01].

Em geral, para que um módulo processador possa operar em uma rede de computadores, devem ser instalados recursos de hardware e software que complementem seus dispositivos e seu sistema operacional local. Em uma rede local, o hardware adicional necessário se constitui, tipicamente, de uma placa de interface de rede e um software, que definimos como *sistema operacional de rede*. Os componentes típicos de um sistema operacional de rede são mostrados na Figura 1 à direita, comparados com o OSI-RM. Tal sistema engloba os seguintes componentes:

• As aplicações cliente-servidor de uso geral;

- Um conjunto de módulos implementando os protocolos;

- Um ou mais módulos de software básico (*drivers*) com implementações de protocolos de comunicação.

Figura 1 - O OSI-RM e um exemplo típico de sistema operacional de rede [TOR01].

O controle e configuração da interface de rede são realizados pelo *driver* da interface de rede, que se comunica com o sistema operacional de rede através de uma interface padronizada.

#### 2.2 A Definição dos Pacotes Ethernet

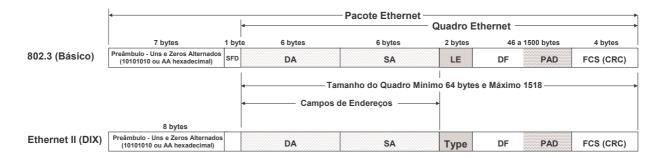

Os termos *pacote*, *quadro* e respectivas siglas serão aqui definidos, procurando manter coerência com o padrão Ethernet IEEE 802.3 [ETH06], pois serão utilizadas constantemente nesta Seção e nas outras que se seguem. Conforme representado na Figura 2, o termo *pacote* (em inglês, *packet*) refere-se à um bloco de dados existente em qualquer nível de abstração, e o termo *quadro* (em inglês, *frame*), quadro de dados ou mensagem, se refere à porção do pacote que é transferida de ou para o nível superior ao subnível MAC.

A Figura 2 detalha os dois tipos de quadros usados na transmissão de dados via tecnologia Ethernet. Há uma diferença sutíl entre o padrão Ethernet II (DIX) anterior à padronização pela IEEE e a norma IEEE 802.3 na estrutura dos seus quadros. No quadro Ethernet II há um campo chamado tipo (*type*), porém no padrão IEEE 802.3 o campo correspondente contém a informação do tamanho do quadro (*length ou LE*). Esta diferença, contudo não causa problemas para implementar o método de transmissão no meio físico, o CSMA/CD (do inglês, *Carrier Sense Multiple Access with Collision Detection*) padrão IEEE 802.3, devido à codificação empregada. A interpretação dos bytes *LE* ou *type* é a seguinte:

Figura 2 - Quadro Ethernet (IEEE 802.3 básico) e Ethernet II (DIX) [TOR01].

- Se o valor é menor ou igual ao tamanho máximo dos dados (1500 bytes), então o campo é interpretado como tamanho de quadro e representa a quantidade de bytes de dados contidos no campo seguinte, o campo de dados (*data field*, *DF*).

- Valores no intervalo entre 1501 e 1535 são considerados impróprios, pois o pacote IEEE 802.3 Básico tem tamanho máximo de 1526 somando-se o conjunto de bytes (1500) e mais as informações de sincronização, cabeçalho e controle de erros. Uma margem de segurança de dez bytes foi inserida para determinar uma diferenciação no campo LE/Type.

- Se o valor é maior ou igual a 1536 bytes (0600 hexadecimal), então o campo indica a natureza do protocolo utilizado e o campo é interpretado como de tipo.

Assim, as interpretações de tamanho e tipo são mutuamente exclusivas. Quando é utilizada a codificação de tipo. Executar a correta operação para o tamanho do quadro é responsabilidade da camada superior ao subnível MAC.

A Figura 2 ilustra os sete campos de um quadro 802.3 (básico), comparado com um quadro Ethernet II DIX, um padrão industrial *de facto* que precedeu a norma IEEE 802.3 [SPU00]. As informações contidas em cada um dos campos do quadro padrão 802.3 são as seguintes:

- **Preâmbulo:** Indica o início da transmissão do quadro. Este campo de 7 bytes é usado para permitir ao circuito de sinalização física (em inglês, *Physical Signaling* ou PLS) sincronizar-se com o quadro recebido. Cada byte deste campo é formado pela sequência 10101010;

- **Delimitador de início de quadro (em inglês,** *Start Frame Delimiter* ou *SFD*): O delimitador é a seqüência binária 10101011 e indica o começo de um quadro imediatamente após os dois últimos bits (11);

- **Endereço destino:** O endereço da estação ou estações, a quem o quadro é destinado (em inglês, *Destination Address* ou DA) e seu tamanho é de 48 bits (6 bytes);

- Endereço fonte: Este campo indica o endereço da estação (em inglês, *Source Address* ou SA) que iniciou a transmissão. Este campo possui tamanho de 48 bits (6 bytes);

- **Tamanho do quadro:** Este campo, de 16 bits (2 bytes), indica o tamanho do quadro (em inglês, *length* ou LE), exceto os campos Preâmbulo e SFD [SPU00]. Para o padrão Ethernet II DIX, este campo é denominado tipo (em inglês, *type*). O campo de tipo contém um código específico de protocolo do quadro;

- **Dados (em inglês,** *Data Field* **ou DF):** Possui um tamanho mínimo de 46 bytes e máximo de 1.500 bytes. Este campo contém os dados a enviar através da rede. Se a quantidade de dados a ser enviada for menos de 46 bytes, então um conjunto de bits de preenchimento (denominados em inglês de *padding* bits ou PAD) é acrescentado ao final dos dados para completar o tamanho

mínimo;

• Seqüência de verificação de quadro: O *Frame Check Sequence* (FCS) implementa um código de verificação de erro do tipo *Cyclic Redundancy Check* (CRC). Este valor é computado como uma função dos conteúdos dos campos endereço destino (DA), endereço fonte (SA), tamanho do quadro (LE) e dados (DF+PAD, quando este último existir). O FCS possui 32 bits (4 bytes) de comprimento.

#### 2.3 A Definição dos Datagramas IP

Uma rede de computadores deve oferecer um sistema de comunicação confiável e transparente. Para isto foi criado um serviço que esconde os limites da camada física de rede, provendo os benefícios de redes virtuais. As redes virtuais são uma abstração utilizada pelos desenvolvedores, permitindo a estes uma total liberdade na escolha de endereços, formato dos pacotes e aplicação de técnicas, independentemente das limitações da rede física.

O endereçamento é um componente crítico na abstração de redes virtuais. Para dar a impressão de uma rede única e uniforme, todos os computadores hospedeiros (do inglês, *host*) devem usar um esquema de endereçamento uniforme. Infelizmente, os endereços físicos não são suficientes, pois uma rede virtual pode englobar múltiplas tecnologias de rede física, cada uma com seu próprio formato de endereçamento. Desta forma, os endereços usados por duas tecnologias podem ser incompatíveis devido aos diferentes tamanhos ou formatos.

Para garantir a uniformidade no endereçamento para todos os hospedeiros, os protocolos da camada de rede definem um esquema de endereçamento independente dos endereços físicos dos dispositivos que estão se comunicando. Mesmo que o esquema de endereçamento na rede virtual seja uma abstração criada por software, os endereços do protocolo são usados como destino e origem da mesma forma que os endereços em uma rede física. Para enviar um pacote através da rede virtual, o transmissor coloca o endereço de destino no pacote e o envia ao software de protocolo para transmissão. Cada computador hospedeiro conhece apenas os endereços virtuais dos outros hospedeiros, comunicando-se através destes endereços sem ter conhecimento da rede física que liga cada um deles.

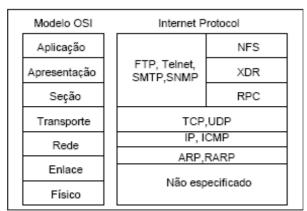

Na pilha de protocolos TCP/IP o esquema de endereçamento é realizado pelo Protocolo Internet (do inglês, *Internet Protocol* – IP), o protocolo de rede virtual mais usado no mundo e base da Internet. O padrão IP especifica que cada hospedeiro tenha um número de 32 bits diferente, conhecido como o Endereço do Protocolo Internet (do inglês, *Internet Protocol Address*), que é comumente abreviado para Endereço IP. Em relação ao modelo OSI-RM o protocolo IP faz, em parte, o papel do nível 3 (Rede) como mostra a Figura 3.

O protocolo IP utiliza uma estrutura de dados conhecida como Datagrama IP (do inglês, *IP Datagram*) para enviar o pacote através da rede virtual. Esta estrutura é formada por um cabeçalho (do inglês, *header*) que contém as informações de controle de para onde e como o pacote vai ser transmitido e um campo de dados ou carga útil (do inglês, *payload*).

A quantidade de dados presente em um datagrama IP não é fixa. O transmissor escolhe uma quantidade de dados apropriada à cada aplicação de camadas superiores. O datagrama IP ainda deverá ser transportado na rede por um protocolo inferior a ele. O caso mais comum em redes computadores é este protocolo o Ethernet. Isso limita a capacidade de dados a serem transmitidos em um pacote IP. No protocolo IP esta limitação é contornada com o uso de fragmentação do

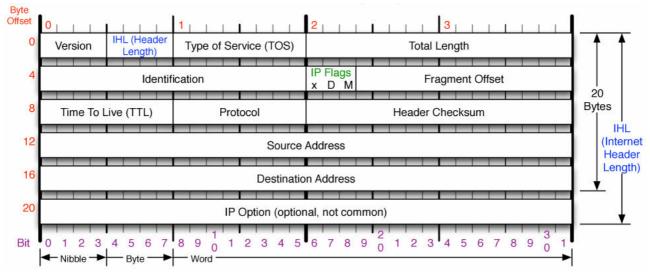

datagrama IP. Quando o tamanho de um datagrama IP excede a capacidade de um quadro da camada inferior, o protocolo IP fragmenta o datagrama maior em partes menores e os transmite como vários datagramas menores. A Figura 4 exibe a estrutura de um datagrama IP mostrando a estrutura do cabeçalho deste.

Figura 3 - Relação dos protocolos da pilha TCP/IP com o modelo OSI [TOR01].

Figura 4 - Estrutura do cabeçalho de um datagrama IP.

O cabeçalho contém informações de roteamento e controle do datagrama, e possui os seguintes campos:

- Versão (*Version*): Este campo identifica a versão do protocolo IP usada no datagrama. Datagramas recebidos com versões não conhecidas devem ser simplesmente ignorados. A versão mais utilizada é a versão 4, mas existe uma versão mais nova, a versão 6, que é utilizada somente em algumas redes locais e nos roteadores principais da internet;

- Tamanho do Header (*Header Length*): Este campo define o comprimento do cabeçalho IP em múltiplos de 4 bytes. O tamanho variável do cabeçalho permite o uso de campos opcionais, mas dificulta o processamento. Desta forma, o uso de cabeçalhos de tamanho não padrão deve ser evitado;

- **Tipo de Serviço** (*Type of Service*): Este campo define a qualidade do serviço (QOS) desejada, mas é ignorado na maioria das implementações. Com o uso deste campo é possível escolher as prioridades de serviço para aplicações do tipo interativas, de transferência em massa ou de

tempo real;

- **Tamanho Total** (*Total Length*): Este campo define o tamanho total, em bytes, do datagrama (ou de um fragmento), incluindo o cabeçalho. Todos os hospedeiros devem aceitar datagramas de, pelo menos, 576 bytes, o valor máximo a ser usado em uma sub-rede pode ser negociado entre os hospedeiros;

- **Identificador** (*Identification*): Este campo define um número único para um datagrama IP que será fragmentado. Cada fragmento do datagrama terá o mesmo identificador do primeiro fragmento;

- *Flags*: *Flags* para a resolução de pacotes fragmentados. Este campo, de 3 bits possui 2 bits relevantes:

- Não Fragmentar (Do not Fragment) que informa que o datagrama não deve ser fragmentado.

- Mais Fragmentos (More Fragments) que indica a existência de mais fragmentos após a posição deste. Ou seja, se este bit não estiver habilitado, este é o último fragmento da cadeia;

- Offset de Fragmento (Fragment Offset): Este campo determina a posição relativa deste fragmento em relação ao datagrama original. Como o campo Flags consome 3 bits (um é reservado), este campo é utilizado sempre em múltiplos de 8;

- **Tempo de Vida (***Time to Live***):** A cada nó (roteador) por onde o datagrama passa, este campo deve ser decrementado de uma unidade. Quando o valor do TTL chega a zero, o datagrama é descartado e uma mensagem enviada ao emissor, através do protocolo ICMP. O objetivo de toda esta operação é evitar que erros nas tabelas de roteamento permitam que alguns datagramas fiquem circulando indefinidamente pela rede;

- **Protocolo** (*Protocol*): Este campo é o identificador do protocolo usado na camada imediatamente acima do IP. Os protocolos mais usados na internet são: TCP, UDP e ICMP;

- Checksum do Cabeçalho (Header Checksum): Este campo garante a integridade do cabeçalho IP, mas não garante a integridade dos dados. Caso haja erro neste, o datagrama deve ser descartado:

- Endereço IP de Origem (*Source IP Address*): Este campo informa o endereço IP da origem do datagrama;

- Endereço IP de Destino (*Destination IP Address*): Este campo informa o endereço IP do destino do datagrama;

- **Opções do IP** (*IP Options*): Este campo permite o uso de serviços extras do protocolo IP. Todas as implementações de IP devem suportar todas as opções válidas;

#### 2.4 A Definição dos Segmentos TCP

Esta Seção examina o protocolo TCP, o protocolo de transporte mais utilizado na pilha de protocolos TCP/IP.

O protocolo TCP utiliza o serviço de datagramas oferecido pelo IP para enviar dados para outro computador, e provê um serviço de entrega de dados confiável para os programas aplicativos.

O TCP deve compensar a perda ou atraso de pacotes ocorridos na rede para garantir uma transmissão eficiente de dados, e precisa fazer isso sem sobrecarregar os protocolos de camadas inferiores ou os roteadores da rede.

Confiança na transmissão é responsabilidade de um protocolo de transporte; aplicações interagem com o serviço de transporte para enviar e receber dados. Na pilha de protocolos TCP/IP, o Protocolo de Controle de Transmissão (do inglês, *Transmission Control Protocol* ou TCP) provê um serviço de transporte confiável. Conseqüentemente, a maioria das aplicações de rede utiliza o TCP.

Do ponto de vista de um programa aplicativo, o serviço oferecido pelo TCP tem sete características principais [COM97]:

- Orientação a Conexões: O TCP provê um serviço orientado a conexão, no qual uma aplicação deve primeiramente requisitar uma conexão com o destino, e só então usar esta conexão para transferir dados;

- Comunicação Ponto-à-Ponto: Cada conexão TCP tem exatamente duas extremidades;

- Completa Confiança: O TCP garante que todos os dados que são enviados pela rede serão entregues exatamente como foram transmitidos, sem nenhum dado faltando ou fora de ordem;

- Comunicação *Full Duplex*: Uma conexão TCP permite que os dados fluam nas duas direções, e permite que o programa aplicativo envie dados a qualquer momento. O TCP pode memorizar dados de entrada e saída nos dois sentidos, sendo possível que a aplicação envie dados e em seguida continue o processamento enquanto os dados estão sendo transmitidos;

- Interface Contínua: Dize-se que o TCP provê uma interface contínua, na qual uma aplicação envia uma sequência contínua de bytes através da conexão. Isto é, o TCP não mantém um registro do que já foi transmitido, e não garante que uma estrutura de dados criada por uma aplicação origem seja entregue em partes de mesmo tamanho que a original na aplicação destino, onde esta estrutura pode ser fragmentada e deverá ser remontada antes de chegar à aplicação destino;

- Início de Conexão Segura: O TCP exige que quando duas aplicações criam uma conexão, ambas devem concordar com esta nova conexão. Pacotes duplicados usados em conexões anteriores não serão considerados respostas válidas, desta forma não irão interferir na nova conexão;

- Fechamento de Conexão Confiável: Um programa aplicativo pode abrir uma conexão, enviar uma quantidade de dados arbitrária, e depois requisitar o fechamento da conexão. O TCP garante a entrega de todos os dados antes de fechar a conexão.

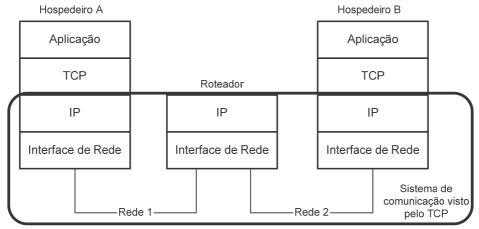

O TCP utiliza o IP para enviar mensagens. Cada mensagem TCP é encapsulada em um datagrama IP, este por sua vez é encapsulado em um, ou mais frames Ethernet que são então transmitidos pela rede. Quando um datagrama chega ao seu destino, o IP passa o seu conteúdo ao TCP. Note que apesar de o TCP usar o IP para enviar mensagens, o IP não lê ou interpreta estas mensagens. Deste modo, o TCP trata o IP como um sistema de pacotes de comunicação, e o IP trata cada mensagem TCP como dados a serem transmitidos. A Figura 5 mostra os diferentes níveis de encapsulamento na transmissão de dados pela rede.

A Figura 6 mostra um exemplo de rede que contém dois hospedeiros e um roteador e ilustra a relação entre os softwares de TCP e IP.

DH - Cabeçalho Ethernet, DT - Ethernet CRC, NH - Cabeçalho IP,

TH - Cabeçalho TCP, AH - Cabeçalho da Aplicação.

Figura 5 - Encapsulamento dos dados e dos diversos protocolos na pilha TCP/IP [TOR01].

Figura 6 - Um exemplo que ilustra a rede na visão do protocolo TCP.

Como mostra a figura acima, o TCP é necessário em cada ponta da conexão virtual de rede, mas não nos roteadores intermediários. Sob o ponto de vista do TCP, toda a rede é um sistema de comunicação que aceita e entrega mensagens sem mudar ou interpretar o conteúdo destas.

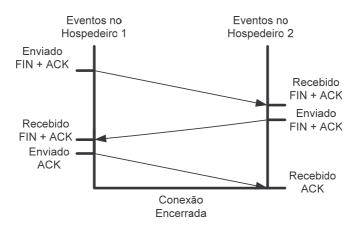

Para garantir que as conexões são estabelecidas e terminadas de forma confiável, o TCP utiliza um handshake de três vias (do inglês, 3-way Handshake) na qual três mensagens são trocadas entre as partes. O TCP usa o termo segmento de sincronização (do inglês, synchronization segment ou SYN segment) para descrever as mensagens no sistema de handshake de três vias usadas na criação de conexões, e o termo segmento de término (do inglês, finish segment ou FIN segment) para descrever as mensagens usadas para fechar uma conexão. A Figura 7 ilustra o handshake de três vias usado para fechar uma conexão, mesmo procedimento utilizado no estabelecimento de conexão.

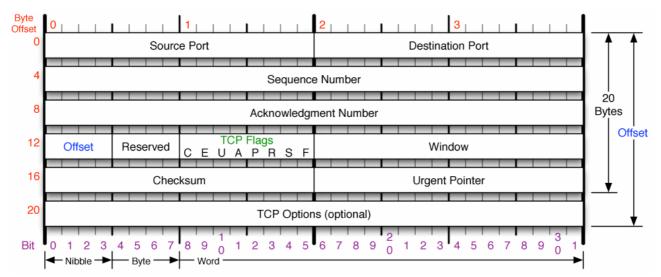

O TCP utiliza um único formato para todas as mensagens, incluindo as mensagens que contêm dados válidos, confirmações, e mensagens que fazem parte do handshake de três vias usado para criar ou terminar uma conexão. O TCP utiliza o termo segmento (do inglês, *segment*) ao se referir a esta mensagem. A Figura 8 ilustra o formato de um segmento.

Figura 7 - O handshake de três vias usado no fechamento de uma conexão.

Figura 8 - Estrutura do cabeçalho de um segmento TCP.

O cabeçalho de um segmento TCP possui os seguintes campos:

- **Porta Origem (Source Port):** Identifica a aplicação de origem;

- Porta Destino (*Destination Port*): Identifica a aplicação de destino;

- **Número de Seqüência** (*Sequence Number*): Identifica a posição deste segmento no fluxo de dados e cada conexão possui um fluxo de dados particular;

- **Número de Confirmação** (*Acknowledgement Number*): Utilizado para confirmar o recebimento de segmentos enviados anteriormente e especifica o próximo segmento aguardado;

- *Offset*: Define o tamanho do cabeçalho em palavras de 32 bits;

- **Reservado** (*Reserved*): Reservado para testes e novas implementações do TCP;

- *Flags*: Possui as informações de conexão do TCP;

- **Janela** (*Window*): Indica o tamanho (disponível) do buffer do receptor e é usado pelo receptor para indicar ao transmissor uma diminuição no fluxo de dados transmitidos;

- Checksum: Contém informações usadas na verificação de erros do protocolo;

- **Ponteiro de Urgência** (*Urgent Pointer*): Usado pela origem para indicar onde se encontra algum dado urgente dentro do segmento;

- Opções (*Options*): Usado para a configuração de opções, se houver;

#### 2.5 A Definição dos Datagramas UDP

O Protocolo de Datagramas de Usuário (do inglês, *User Datagram Protocol*, ou *UDP*) pode ser descrito de forma análoga ao TCP. O UDP provê às aplicações acesso direto ao serviço de entrega de datagramas, como o serviço de entrega que o IP provê. O UDP é pouco confiável, sendo um protocolo não orientado a conexão. O termo "pouco confiável" significa que não há técnicas no protocolo para confirmar que os dados chegaram ao destino corretamente.

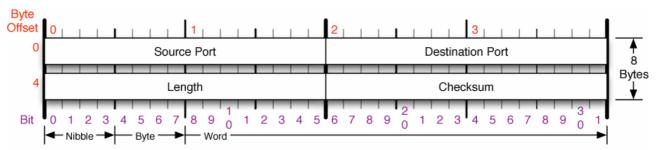

O UDP faz a entrega de mensagens independentes, designadas por datagramas, entre aplicações ou processos, em sistemas hospedeiros. A entrega não é confiável, porque os datagramas podem ser entregues fora de ordem ou até descartados. O formato de um datagrama UDP é bem simples, ele contém um pequeno cabeçalho e um campo de dados. A Figura 9 ilustra o formato de um datagrama UDP.

Figura 9 - Formato do cabeçalho de um datagrama UDP.

O cabeçalho UDP possui os seguintes campos:

- Porta Origem (Source Port): Identifica a aplicação de origem;

- Porta Destino (*Destination Port*): Identifica a aplicação de destino;

- Comprimento (*Length*): Contém um contador de bytes no datagrama UDP. O valor mínimo é oito, sendo este só o comprimento do cabeçalho;

- *Checksum*: Contém informações usadas na verificação de erros do protocolo.

#### 2.6 A Definição das Mensagens ICMP

Esta Seção examina um protocolo de relatório de erros que é integrado ao protocolo IP. São revisados os erros básicos que podem ser informados, e é explicado como e quando estas mensagens de erro são enviadas.

O serviço IP é um serviço pouco confiável, pois os datagramas podem ser descartados, duplicados, atrasados ou entregues fora de ordem durante seu trajeto entre dois hospedeiros. Desta forma, é necessário dispor de serviços e mecanismos que realizem a detecção de erros.

Problemas menos graves que a transmissão de erros resultam em condições de erro que podem ser informadas. Por exemplo, suponha que alguns caminhos físicos na rede venham a falhar, dividindo a rede em duas partes e sem nenhuma conexão entre elas. Um datagrama enviado de um hospedeiro em uma parte com destino a outra parte não poderá ser entregue.

A pilha de protocolos TCP/IP inclui um protocolo usado pelo IP para enviar mensagens de erro quando situações como a descrita acima ocorrem: o Protocolo de Controle de Mensagens da Internet (do inglês, *Internet Control Message Protocol* ou *ICMP*). Este protocolo é necessário na implementação padrão do IP. O ICMP e o IP são dois protocolos co-dependentes, o IP utiliza o ICMP quando precisa transmitir uma mensagem de erro e o ICMP utiliza o IP para transportar suas

mensagens.

O ICMP define cinco mensagens de erro e quatro mensagens informais. As cinco mensagens de erro no ICMP são:

- **Dissipador de Fonte** (*Source Quench*): Um roteador envia uma mensagem dissipadora de fonte a cada vez que este recebeu tantos datagramas que não possui mais espaço de armazenamento. Um roteador que tenha atingido seu limite de armazenamento deve descartar todos os datagramas que são recebidos. Quando descarta um datagrama, o roteador envia uma mensagem dissipadora de fonte ao hospedeiro que criou o datagrama. Quando receber uma mensagem dissipadora de fonte, o hospedeiro precisa reduzir a sua taxa de transmissão;

- **Tempo Excedido** (*Time Exceeded*): Uma mensagem de tempo excedido é enviada em dois casos:

- toda vez que um roteador reduz o campo tempo de vida do datagrama e este chega a zero, o roteador então descarta o datagrama e envia uma mensagem de tempo excedido ao hospedeiro de origem;

- Quando o tempo de remontagem (do inglês, *reassembly*) expirar antes que todos os fragmentos de um dado datagrama tenham sido recebidos;

- **Destino Inatingível** (*Destination Unreacheable*): Cada vez que um roteador determinar que um datagrama não pôde ser entregue ao seu destino final, o roteador envia uma mensagem de destino inatingível ao hospedeiro que criou o datagrama. A mensagem especifica se o hospedeiro está inatingível ou se a rede na qual este está conectado está inatingível. Em outras palavras, esta mensagem de erro distingue se aquela sub-rede está desconectada do resto da rede (e.g., devido a queda de um roteador) ou o caso em que aquele hospedeiro em particular está temporariamente fora do ar (e.g., devido ao hospedeiro estar desligado).

- Redirecionamento (*Redirect*): Quando um hospedeiro cria um datagrama destinado à uma rede remota, este envia o datagrama a um roteador, o qual encaminha este datagrama ao seu destino. Se o roteador determina que o hospedeiro lhe enviou incorretamente um datagrama e este precisa ser enviado a um roteador diferente, o roteador que recebeu o datagrama utiliza uma mensagem de redirecionamento para que o hospedeiro corrija a rota deste. A mensagem de redirecionamento pode especificar uma mudança de um hospedeiro específico ou uma mudança de rede; a ultima opção é a mais comum;

- Necessita Fragmentação (*Fragmentation Required*): Um hospedeiro ao criar um datagrama pode especificar no cabeçalho que este não pode ser fragmentado. Se um roteador verifica que este datagrama é maior que a MTU (do inglês, *Maximum Transmission Unit*) da rede em que está sendo transmitido, ele pode enviar uma mensagem Necessita Fragmentação ao transmissor, e então descarta o datagrama.

Além destas mensagens de erro, o ICMP define as seguintes mensagens informativas:

- **Pedido/Resposta de Eco** (*Echo Request/Reply*): Um pedido de eco pode ser transmitido ao software ICMP de qualquer computador. Em resposta à um pedido de eco, o software ICMP é obrigado a enviar uma mensagem de resposta de eco. A resposta leva o mesmo conjunto de dados do pedido de eco.

- Pedido/Resposta de Máscara de Endereço (Address Mask Request/Reply): Um hospedeiro, na sua inicialização, transmite a todos um pedido da máscara de endereço, e um roteador que

recebe este pedido envia uma resposta da máscara de endereço que contém a máscara de subrede (32-bits) em uso.

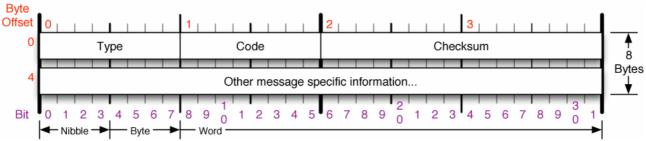

A mensagem ICMP é formada por um cabeçalho e um campo de dados. A Figura 10 ilustra o formato do cabeçalho de uma mensagem ICMP.

Figura 10 - Formato do cabeçalho de uma mensagem ICMP.

O cabeçalho de uma mensagem ICMP possui os seguintes campos:

- **Tipo** (*Type*): Especifica o tipo da mensagem ICMP;

- Código (Code): Qualifica a mensagem ICMP;

- Checksum: Contém informações usadas na verificação de erros do protocolo;

- Outras informações específicas da mensagem: Este campo pode conter mais informações da mensagem como, por exemplo, a máscara de sub-rede em uma mensagem do tipo *Address Mask Reply*.

### 3 NIDS – Sistemas de Detecção de Intrusão em Redes

Com o barateamento dos computadores pessoais, a interconexão entre eles, ou uma rede de computadores, tornou-se uma entidade vital no dia-a-dia. Todo tipo de informação trafega por esta rede, desde transações financeiras, informações esportivas, entretenimento, telefonia e até informações militares. Desta forma, a rede tornou-se alvo de grande cobiça por informações importantes. Esta cobiça por informação leva a rede a sofrer diversas tentativas de acesso indevidas, tentativas estas conhecidas como ataques.

Existem diversos tipos (ou técnicas) de ataques em redes de computadores. Alguns visam a extração de informação, alguns visam a paralisação de um determinado serviço ou máquina da rede, outros visam a conexão com um determinado serviço ou máquina da rede, etc. Estes ataques podem estar presentes em diferentes protocolos da rede. Existem ataques IP, ICMP, TCP, UDP entre outros.

Os ataques de redes que são focados no presente Trabalho de Conclusão são aqueles em que o código de ataque malicioso está presente no conteúdo (em inglês, *content*) do pacote nos protocolos IP, ICMP, TCP e UDP. Estes ataques em particular são detectados através de um comparador de padrões.

A necessidade de garantir o funcionamento seguro de sistemas de computação tem exigido esforços crescentes, no sentido de evitar o que se convencionou chamar de intrusão, ou seja, o uso não autorizado ou o mal uso de um sistema de computação [PTA03][KEM02]. Isto levou à criação de sistemas de detecção de intrusão ou IDSs (*Intrusion Detection Systems*), sistemas computacionais especializados na proteção de outros sistemas. Como as redes são um meio essencial para o acesso aos componentes de um sistema de computação, a vigilância específica sobre o tráfego das redes pode resguardar a segurança de toda a instalação. Para este fim foram criados os NIDS, IDSs especializados na vigilância sobre o tráfego de redes.

Dentre as tarefas de um NIDS destacam-se as seguintes:

- Captura de pacotes um NIDS tem que capturar pacotes da rede para realizar uma análise e determinar a presença de ameaça, ou ataque, no seu conjunto de dados.

- Comparação de padrões é a tarefa principal do sistema e a que consome maior poder computacional. Cada byte do pacote deve ser confrontado com milhares de regras para determinar um provável ataque.

#### 3.1 Snort - Descrição de operação

Snort [SNO06] é um NIDS capaz de realizar análise de tráfego em tempo real, seleção e registro de pacotes em redes TCP/IP. O Snort pode realizar identificações de protocolo, busca ou comparação de conteúdo, e pode ser utilizado para detectar uma variedade de ataques e *probes* (análises remotas ou sondagens). Por ser um sistema em software de fonte aberto [LAW02], o Snort recebe contribuições de programadores e especialistas em segurança de todo o mundo. Desde 1998, quando foi lançado, tem recebido constante atualização de seus algoritmos, de sua estrutura interna e de sua capacidade de identificar novos tipos e variantes de intrusões.

O Snort utiliza os recursos oferecidos pela biblioteca libpcap [TCP03], que fornece

monitoramento de pacotes (*packet sniffing*) em modo promíscuo. O modo de rede promíscuo é a configuração da interface de rede na qual todos os pacotes que nesta chegam são capturados, independente se este pacote é ou não destinado a este hospedeiro. A biblioteca *libpcap* foi escrita como parte de um programa maior, chamado *TCPDump* [TCP03], utilizado para decodificar, visualizar ou registrar pacotes em uma rede IP.

O Snort realiza detecção baseada em regras, sendo este um dos motivos que lhe proporcionam flexibilidade. As regras permitem configurar o sistema de detecção conforme requisitos de desempenho ou tipo de tráfego. O Snort permite a identificação de protocolos, de assinaturas e de anomalias em protocolos. Por meio de regras, pode-se especificar a detecção de uma condição complexa, e a partir daí determinar uma reação.

Snort inclui *plug-ins* em sua arquitetura como estratégia de flexibilidade. Um uso importante desta modularização é no tratamento que pode ser dado aos alertas resultantes da atividade do Snort como um NIDS. Como o número de alertas e registros pode tornar-se muito grande em redes sob ataque, alguma forma de classificação e tratamento automático adequado para cada situação tornase necessária. Entretanto, o número elevado destas situações não permite um tratamento padronizado. Daí a importância da modularização, fazendo com que cada situação possa ser tratada de maneira particular. A modularização é importante igualmente para prover tratamento adequado aos diferentes regimes de tráfego encontrados na aplicação do Snort.

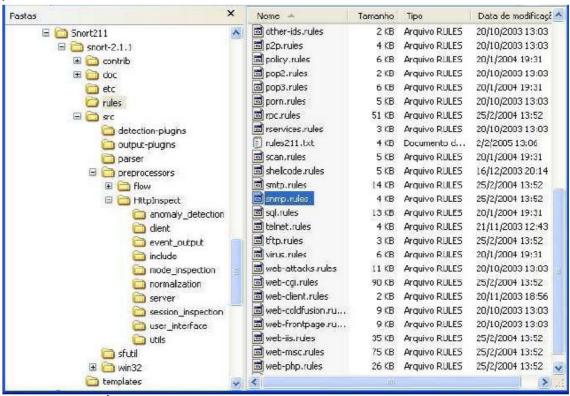

Snort é fornecido junto com uma coleção de regras, que inclui regras desativadas como forma de documentação. O site do Snort (http://www.snort.org) mantém um banco de dados com informações sobre todas as regras já publicadas. Ao ser instalado, o Snort gera um diretório onde são instaladas todas as regras conhecidas. Neste diretório as regras são agrupadas por afinidade, em arquivos cujo nome caracteriza sua aplicação. A Figura 11 mostra uma árvore de diretórios de uma instalação típica do Snort, com detalhe no diretório de regras (diretório *rules*) e parte de seu conteúdo.

Um arquivo de configuração, usualmente chamado de *snort.conf*, especifica quais dos arquivos de regras devem ser utilizados quando o Snort operar como um NIDS. Este arquivo também configura a modularização do Snort, ativando *plug-ins* seletivamente.

O Snort aplica-se a três principais usos:

- Monitoramento de pacotes;

- Registra de pacotes;

- NIDS

A função de monitor de pacotes (*sniffer*), ativada através da opção "-v" na linha de comando, permite visualizar os pacotes coletados da rede na tela.

Como registrador de pacotes (*logger*) a coleta de pacotes é direcionada para um arquivo, para futura análise ou uso como padrões de tráfego, por meio da reprodução destes pacotes na rede. A opção de linha de comando "-l" seguida do nome de um arquivo destino ativam este modo e permitem ao Snort registrar neste arquivo o tráfego da rede.

Como um NIDS, o nome do arquivo de configuração (*snort.conf*), deve ser adicionado na linha de comando. Este arquivo contém a descrição de componentes opcionais que o Snort deverá ativar para esta função. Entre estes estão os conjuntos de regras de detecção e os pré-processadores

que são responsáveis pela geração dos alertas esperados de um NIDS. Em aplicações comerciais o Snort pode ser encontrado fazendo uso exclusivo do hardware de um servidor, associado a uma máquina *firewall* ou a um roteador. Quando não há restrições de investimento, aplica-se um NIDS para cada sub-rede, associa-se o Snort ao *firewall* e aos roteadores da rede

Figura 11 - Árvore de diretórios de instalação do Snort e trecho do diretório das regras.

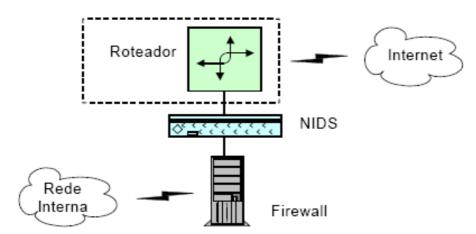

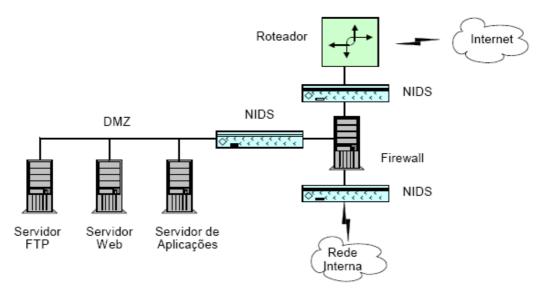

Em instalações mais simples, como a apresentada na Figura 12, a rede interna é protegida por um *firewall* e um NIDS é colocado à frente deste, ou associado a este, antes da rede externa. Muitas vezes, nesta topologia, um roteador é ainda posicionado à frente do NIDS.

Figura 12 - Arquitetura simples com NIDS e roteador opcional.

Redes que ofereçam ao acesso externo uma das chamadas zonas desmilitarizadas (DMZ), acessam a rede externa por meio de um roteador com NIDS, conforme mostra a Figura 13. Uma zona desmilitarizada ou DMZ corresponde ao segmento ou segmentos de rede, parcialmente protegido, que se localiza entre redes protegidas e redes desprotegidas e contém todos os serviços e informações para clientes ou públicos. Um *firewall* conectado ao roteador, pelo lado interno,

distribui tráfego à DMZ e à rede interna por meio de respectivos NIDS adicionais. Neste caso se utiliza o Snort tanto na rede interna quanto na DMZ, pois podem existir ataques específicos a ambas as redes.

Figura 13 - Rede com DMZ Firewall e Snort.

#### 3.2 Snort - O formato das regras

Para ilustrar o formato básico das regras aceitas pelo Snort, apresenta-se a seguir uma regra que detecta um ataque FTP. As regras do Snort são escritas em formato texto em uma única linha, e constituem-se de duas sessões: o cabeçalho e as opções.

- O cabeçalho da regra: alert tcp \$EXTERNAL\_NET any -> \$HOME\_NET 21

- As opções da regra: (msg: "FTP EXPLOIT wu-ftpd 2.6.0 site exec format string overflow Linux"; flow:to\_server, established; content:"|31c031db31c9b046cd8031c031db|"; reference:bugtraq,1187; reference:cve,CAN-2000-0573; reference arachnids,287; classtype: attempted admin; sid:344; rev4;)

A sintaxe usada no cabeçalho das regras compreende:

- alert: Formato utilizado para a saída. Os formatos de saída são: alert, log, pass, dynamic e activate.

- TCP: Protocolo em uso. Este campo pode aceitar os valores: TCP, UDP, IP e ICMP.

- **\$EXTERNAL NET**: Endereço IP de origem.

- any: Porta de origem.

- ->: Direção do fluxo de dados. Neste caso, de \$EXTERNAL\_NET vindo de qualquer porta para \$HOME NET na porta 21.

- **\$HOME NET**: Endereço de destino.

- 21: Porta destino.

O principal componente nas opções da regra é o seu conteúdo (do inglês, *content*). O campo *content* "|31 C0 31 DB 31 C9 B0 46 CD 80 31 C0 31 DB|" é comparado com o pacote em análise usando um algoritmo de comparação de cadeias de caracteres.

## 4 Implementação de NIDS em Hardware

Este Capítulo descreve inicialmente o SPP-NIDS (*Sea of Processors Platform for Network Intrusion Detection System*), uma implementação de NIDSs desenvolvida no trabalho de Mestrado de Luís Mieres Caruso [CAR05a], e utilizado como base para o desenvolvimento do presente Trabalho de Conclusão. A segunda parte do Capítulo apresenta um NIDS em hardware, comercial, com funções similares à proposta deste trabalho.

#### 4.1 SPP-NIDS – Um NIDS em Hardware

A plataforma SPP-NIDS é uma implementação hardware-software de um NIDS, com suporte a regras do Snort. Esta plataforma não foi integrada com a rede externa, nem com sistemas de gerenciamento, o que é parte da contribuição deste trabalho, e será apresentado no Capítulo 5. O SPP-NIDS é viável para situações reais de detecção de intrusão de rede, pois:

- O sistema é escalável. Adicionar novas unidades de comparação ao projeto é uma questão de código HDL parametrizável;

- O número de regras que o sistema suporta é alterado pela reprogramação do banco de regras na memória de um processador;

#### 4.1.1 Visão Geral da arquitetura do SPP-NIDS

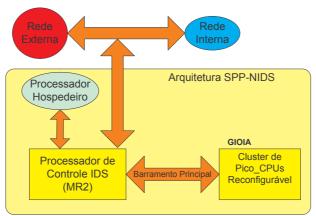

O diagrama de blocos da plataforma e suas interfaces externas estão descritas na Figura 14 [CAR05b]. A arquitetura SPP-NIDS [CAR05b] é composta por um processador de controle IDS, um co-processador dedicado reconfigurável (cluster GIOIA na figura), um processador hospedeiro e interfaces para um enlace que conecta as redes externa e interna.

Figura 14 – Diagrama de blocos da arquitetura do SPP-NIDS.

O módulo principal do sistema é o co-processador dedicado reconfigurável chamado GIOIA. GIOIA é um *cluster* de processadores muito simples e idênticos, personalizados para comparação de regras. Cada um destes processadores simples é chamado de pico-CPU. Este co-processador foi projetado especificamente para realizar a comparação de padrões para aplicação das regras do Snort. Conectando pico-CPUs em paralelo obtém-se um determinado desempenho, o qual é escalável conforme o número de pico-CPUs.

O processador de controle IDS, na SPP-NIDS, é chamado de MR2. Ele é responsável pela inserção de regras na memória de cada pico-CPU, e pela monitoração e controle do GIOIA. Ele também é responsável pela interação com o processador hospedeiro, e com as redes interna e externa. O MR2 [CAL04] é um processador com organização Harvard que implementa um conjunto parcial de instruções do MIPS 2000, uma versão da arquitetura do MIPS I <sup>TM</sup>.

O processador hospedeiro é tipicamente um equipamento externo (computador), responsável pela inicialização do processador de controle IDS e do cluster GIOIA.

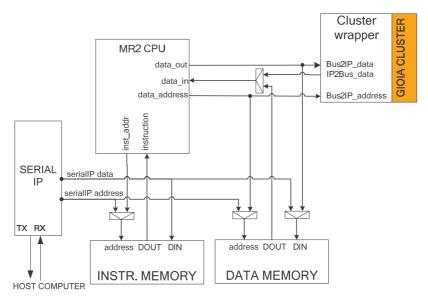

#### 4.1.2 Estratégia de prototipação da SPP-NIDS

A arquitetura SPP-NIDS foi proposta em [CAR05a]. O primeiro protótipo de hardware deste sistema foi desenvolvido visando à participação no Xilinx Student Contest de 2005, cujas regras fixavam o uso da plataforma de prototipação Digilent Spartan-3 System Board para o projeto [XIL06]. Devido às restrições de entrada/saída de dados imposta por esta plataforma de prototipação, algumas alterações no projeto inicial da arquitetura do SPP-NIDS foram realizadas. Esta Seção descreve estas alterações e o resultado final do sistema prototipado.

Primeiramente, o kit Spartan-3 não contém uma interface de rede incorporada, como por exemplo, um módulo PHY Ethernet acoplado a um conector RJ-45. Mesmo se um módulo PHY estivesse disponível, o módulo MAC Ethernet e a implementação da pilha IP ocupariam uma grande parte do FPGA Spartan-3 de duzentas mil portas lógicas equivalentes da placa, inviabilizando a implementação do sistema SPP-NIDS no mesmo dispositivo.

Desta forma, o comportamento da rede é emulado, usando uma parte da memória de dados do MR2, contendo pacotes IP que são lidos por rotinas especializadas de software executadas no processador MR2. Ambas as memórias de dados e instruções são implementadas com Block RAMs internas ao FPGA.

Outra característica do protótipo implementado é que o processador hospedeiro é de fato um computador PC conectado à plataforma de prototipação via interface serial, usando um protocolo compatível com o padrão RS-232. Esta interface permite ao hospedeiro reinicializar e parar o processador MR2, além de permitir a carga da memória de instruções do MR2 com o software de gerência do cluster GIOIA e a carga da memória de dados do MR2 com as regras do Snort que serão enviadas a cada pico-CPU e pacotes IP que emulam o comportamento da rede. O hospedeiro ainda utiliza a interface serial para receber informações sobre tentativas de invasão nos pacotes IP.

No protótipo, o computador hospedeiro não foi utilizado para o envio de pacotes reais ao sistema, dada à baixa velocidade da interface serial. Como o objetivo do protótipo era validar o módulo de comparação do cluster GIOIA, a utilização de uma interface muito mais lenta que uma interface de rede real invalidaria o sistema.

#### 4.1.3 A estrutura do protótipo SPP-NIDS

A Figura 15 apresenta a estrutura do protótipo da arquitetura SPP-NIDS. O cluster GIOIA é mapeado na memória de dados do processador, utilizando os endereços mais altos da memória. O acesso ao cluster é realizado via operações de escrita e leitura na memória do MR2.

Figura 15 – Estrutura geral do protótipo da plataforma SPP-NIDS.

As Seções a seguir descrevem a pico-CPU e cada um dos módulos no protótipo do sistema SPP-NIDS.

#### 4.1.4 A pico-CPU

A função da pico-CPU é verificar se certos padrões (chamados de regras, no Snort) ocorrem em alguma seção do tráfego de entrada da rede. As pico-CPUs armazenam em memórias RAM internas os padrões com os quais o tráfego da rede deve ser comparado. O uso de memória RAM para armazenar os padrões de ataque concede à pico-CPU sua propriedade de reconfigurabilidade. Esta memória foi implementada com um bloco de memória RAM dupla porta (do inglês, *Dual Port RAMs* ou *DPRAMs*) presente no FPGA (*Block Select RAMs* ou *BRAMs*). Já que o Snort possui um conjunto de regras em constante evolução, a reconfiguração é uma das principais características na plataforma SPP-NIDS. Sempre que o Snort disponibilizar um novo conjunto de regras, estas poderão ser imediatamente adicionadas ao SPP-NIDS, bastando atualizar a memória de dados do MR2.

Conforme ilustrado na Figura 16, as memórias *DPRAMs* armazenam subconjuntos do total dos padrões de comparação, organizados em classes (TCP, UDP, IP e ICMP). Os padrões serão armazenados seqüencialmente e são acessados byte a byte. As *DPRAMs* são organizadas em 3 regiões:

- O bloco de registros contém as informações de acesso e controle de cada padrão (Regra). Cada registro contém quatro campos: endereço inicial do padrão na memória (E1 cx py), número de bytes do padrão (T cx py), identificação do padrão (ID cx py) e estado da comparação (S cx py). O estado da comparação (S cx py) é um contador, que é incrementado a cada comparação positiva entre um byte da carga útil (payload) e o padrão em comparação.

- O bloco de vetores armazena os endereços correspondentes ao primeiro registro de cada classe (Protocolo). Desta forma, cada classe pode ter um número arbitrário de registros.

- O bloco de padrões armazena os padrões. Este bloco contém diversos sub-blocos, um para cada padrão armazenado.

A divisão de classes adotadas coincide com a divisão de protocolos reconhecidos pelo Snort quais sejam: TCP, UDP, ICMP e IP.

Figura 16 - Organização das memórias DPRAMs utilizadas pelas pico-CPUs.

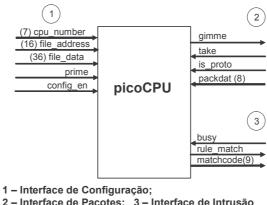

A Figura 17 mostra o conjunto de sinais de entrada/saída de dados e controle de uma pico-CPU. A interface de configuração (índice 1 na Figura 17) permite a carga das regras na memória interna da pico-CPU. Esta configuração é realizada pelo processador MR2. Todas as pico-CPUs dividem um mesmo barramento de configuração e cabe ao sinal cpu number (número único para cada pico-CPU) ditar qual pico-CPU será configurada por vez. Os sinais file address e file data correspondem aos barramentos de endereços e dados, respectivamente. Os sinais prime e config en, quando ativos, indicam que o barramento de configuração está sendo utilizado.

2 - Interface de Pacotes; 3 - Interface de Intrusão

Os valores entre parênteses indicam o número de bits de cada barramento.

Figura 17 - Conjunto de sinais de entrada/saída de dados e controle de uma pico-CPU.

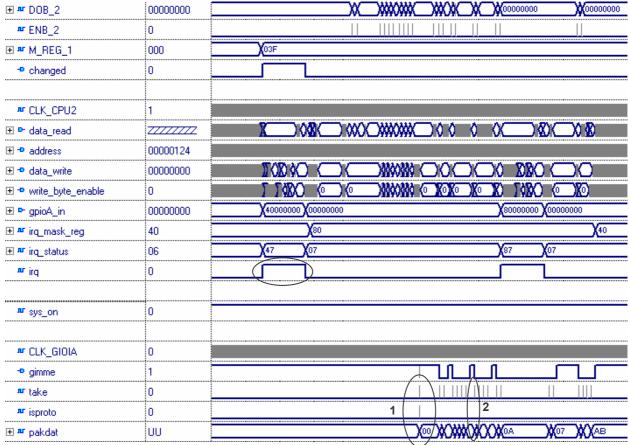

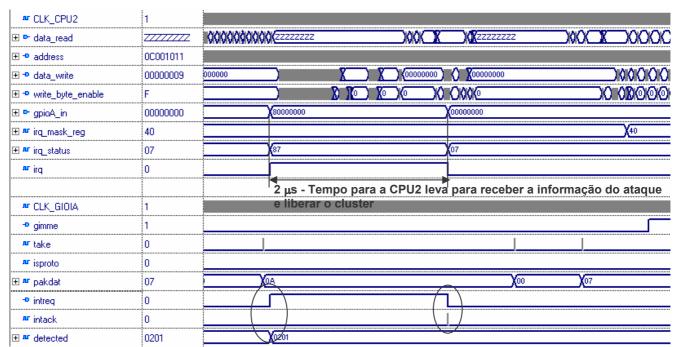

A interface de pacotes (índice 2) recebe os dados de entrada da rede. O sinal *gimme* é usado pela interface de pacotes para descobrir se a pico-CPU está ociosa, e desta forma pronta para processar um novo byte de dados. Os sinais take, is proto e pakdat, são usados para o controle de transferência de novos dados à pico-CPU. Quando o sinal is proto é ativado, indica o início de um novo pacote que será enviado à pico-CPU.

A interface de intrusão (índice 3) permite que a pico-CPU informe ao processador MR2 a detecção de um provável ataque à rede. A ocorrência de um ataque é indicada pela ativação do sinal *rule\_match* e o número da regra do Snort que foi acionada naquela pico-CPU é informado no barramento *matchcode*. Se o sinal *busy* for ativado, a pico-CPU deve manter o *matchcode* estável até que o processador de controle IDS (MR2) libere a sua operação.

Em linhas gerais, uma pico-CPU implementa um algoritmo que pode ser descrito como dois laços aninhados. O laço externo é responsável pela amostragem de todos os caracteres de um pacote, um a um. O laço interno compara cada caractere amostrado com um dos bytes de todas as regras disponíveis nesta pico-CPU. Uma dentre quatro possibilidades pode ocorrer, durante a comparação de um caractere amostrado e um byte de alguma das regras:

- 1. Sem acerto, com o *ponteiro de regra*<sup>1</sup> no início da regra (significa que o campo *S cx py* na Figura 17 permanece com valor em zero), neste caso nenhuma modificação de estado ocorre nas DPRAMs;

- 2. Acerto, sem que esteja no final da regra. Neste caso o ponteiro de regra deve ser adiantado em uma posição na regra (incremento no campo *S cx py*);

- 3. Sem acerto, mas comparações anteriores fizeram o ponteiro de regra avançar na regra. Neste caso o ponteiro deve ser reinicializado à posição de início;

- 4. Acerto, com o ponteiro de regra no último byte da regra (campo *S cx py* igual ao campo *T cx py*), neste caso o sinal rule\_match é ativado informando a ocorrência de um ataque.

A situação padrão é a do item 1 acima, executada em um ciclo de relógio. As situações 2 e 3 levam dois ciclos de relógio para serem executadas. A situação 4 corresponde a uma detecção de regra. O tratamento desta situação depende da CPU de controle IDS e do tamanho do cluster GOIA. Já que as detecções são armazenadas, ocorre pouca perda de desempenho no caso de detecção de ataques.

Como um estudo de caso de requisitos de desempenho, considere-se um tempo médio de 1,5 ciclos relógio para processar cada caractere em um pacote ( $p_t$ ), e uma dada pico-CPU trabalhando a 200 MHz (f) com um conjunto de 20 regras ( $n_r$ ). A vazão de dados ( $T_p$ ) excede 53 Megabits por segundo (Mbps), o que pode ser calculado com a equação  $T_p = (f * 8)/(p_t * n_r)$ . A constante 8 representa o número de bits em um caractere.

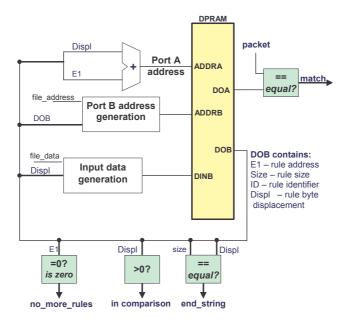

A Figura 18 ilustra o bloco de dados da pico-CPU, uma implementação centrada em uma RAM de dupla porta (DPRAM ou Dual Port RAM). Durante o processo de configuração, os dados são carregados na DPRAM usando a interface de configuração descrita anteriormente.

O primeiro byte de um pacote (sinalizado pelo sinal *is\_proto*, vide Figura 18) é a informação de cabeçalho, definindo o protocolo utilizado (IP, ICMP, TCP, UDP). Este byte inicializa o endereço da porta B (ADDRB), que é um ponteiro para um conjunto de *descritores de regras* referente ao protocolo do pacote em análise. Cada descritor de regras, presente na saída DOB da DPRAM contém quatro campos, três fixos e um variável. Os três campos fixos são: *E1*, o endereço do início da regra; *size*, o número de bytes presentes na regra; *ID*, o identificador único de cada regra. O campo variável é chamado de *Displ*, que representa o deslocamento nos bytes da regra a partir do seu início. A saída da porta A na DPRAM é a leitura da posição de memória do endereço obtido pela soma de E1 e *Displ* como descrito pela Figura 18. Quando a saída da porta A é igual ao

\_

<sup>&</sup>lt;sup>1</sup> Ponteiro de regra indica na memória de padrões a regra em comparação.

byte do pacote corrente, um acerto (match) é obtido.

Figura 18 – Estrutura interna do bloco de dados de uma pico-CPU.

Se um acerto não ocorrer (*match* = 0) e a regra estava no modo de comparação (sinal *in\_comparison* > 0), o campo *Displ* é reinicializado à zero. Se um acerto ocorrer e o campo *Displ* é igual ao tamanho da regra (size) o sinal *end\_string* é ativado, indicando a detecção de um ataque. Se um acerto ocorrer, mas o final da regra ainda não foi atingido o sinal *Displ* é incrementado. Quando todas as regras foram verificadas, o sinal *no\_more\_rules* é ativado, liberando a pico-CPU para receber novos bytes a serem comparados.

#### 4.1.5 O cluster GIOIA

O Snort realiza a separação das regras a serem comparadas por protocolo. Desta forma, o software irá realizar comparações com um conjunto de regras menor do que o total de regras. O Snort na sua versão 2.11[SNO06] separa suas regras em quatro protocolos principais: IP, TCP, UDP e ICMP. O número de regras por protocolo presentes no Snort versão 2.11 é descrito na Tabela 1. O conjunto de regras presentes no Snort é atualizado freqüentemente, e o maior conjunto de regras pertence ao protocolo TCP. Estas regras podem ser subdivididas em subclasses, como por exemplo, filtros de endereços IP. Como o cluster GIOIA foi desenvolvido para dar suporte ao conjunto de regras do Snort, este também possui regras nos quatro protocolos citados acima. Um NIDS operando sobre uma rede 100 Mbps, deveria comparar cada dado recebido contra 1784 regras no intervalo entre dois bytes: 80 ns. Este desempenho é inatingível quando executando em software, justificando a implementação em hardware dedicado.

Tabela 1 – Número de regras por protocolo no Snort v.2.11.

| Protocolo | Número de Regras |

|-----------|------------------|

| TCP       | 1784             |

| UDP       | 165              |

| IP        | 44               |

| ICMP      | 131              |

| TOTAL     | 2124             |

|           |                  |

Um NIDS de qualidade deve ser capaz de comparar cada caractere de entrada da rede contra, no mínimo, quarenta e quatro regras (que equivalem ao menor grupo de regras de um determinado protocolo) no tempo entre duas recepções de caracteres na rede. Este limite estabelece um requisito

mínimo de desempenho no projeto para o cluster GIOIA.

Da mesma forma que as pico-CPUs, o cluster possui três grupos de sinais, implementando as três interfaces distintas de cada pico-CPU:

- Interface de configuração responsável pela carga das regras do Snort no cluster;

- Interface de pacotes responsável pela recepção dos dados extraídos da rede;

- Interface de detecção de intrusão ou simplesmente interface de intrusão responsável pela sinalização de ataques ao processador de controle IDS.

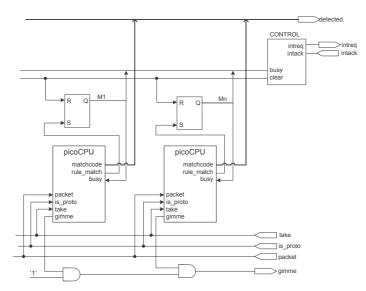

A descrição das interfaces acima é a mesma da Seção 4.1.4. A Figura 19 mostra a interface externa e a organização interna do cluster GIOIA, abstraindo a interface de configuração.

Figura 19 – Interface interna do cluster e a interface com a CPU de controle IDS.

A interface de pacotes pode receber um novo caractere somente se todas as pico-CPUs estiverem livres para processar este novo caractere. O sinal *gimme* é usado para informar esta condição das pico-CPUs. Esta é a razão pela qual o cluster precisa estar balanceado na distribuição de regras de suas pico-CPUs, de tal forma que os tempos de processamento de cada pico-CPU sejam aproximadamente idênticos, reduzindo a ociosidade das pico-CPUs.

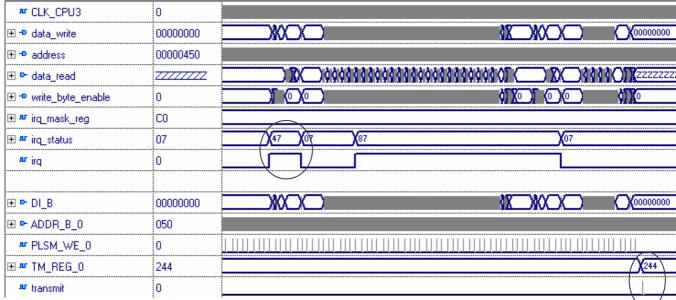

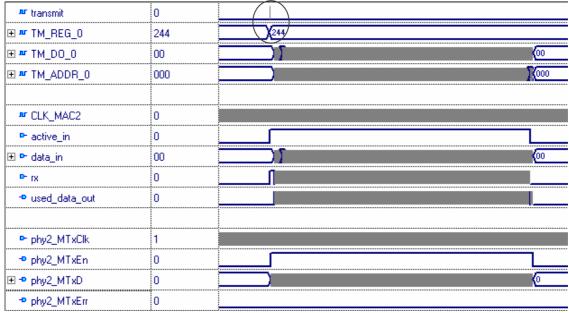

Quando uma pico-CPU detecta um ataque, o sinal *rule\_match* é ligado, ativando o flip-flop de detecção correspondente (um dos flip-flops de M1 a Mn). Quando um dado flip-flop de detecção é ativado, um sinal de *busy* é gerado para a pico-CPU correspondente, travando esta. A unidade de controle do cluster realiza uma varredura *daisy-chain* em todos os registradores de detecção, procurando qual pico-CPU detectou um ataque. Quando um ataque é detectado, um sinal de interrupção é gerado para o processador MR2 e o código do ataque encontrado (chamado de *matchcode*) é armazenado em um registrador do cluster (não mostrado na Figura 19). Ao final desta operação todo o cluster é liberado através do sinal *clear*, desta forma a pico-CPU que detectou o ataque e estava travada é liberada e volta a sua operação normal. O tempo máximo que uma pico-CPU fica travada e não realiza seu algoritmo de detecção é, em ciclos de relógio, igual ao número de pico-CPUs no cluster menos um. O processador MR2, ao realizar o tratamento da interrupção gerada pelo cluster, salva o código do ataque que estava armazenado em registrador e libera a varredura *daisy-chain* com um sinal de *int ack*.

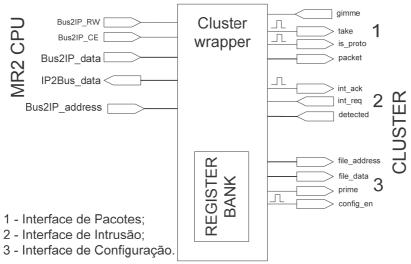

#### 4.1.6 O wrapper do cluster GIOIA

O *wrapper* do cluster tem a função de adaptar os sinais para o barramento de dados do processador de controle IDS, e está ilustrado na Figura 20. Esta adaptação ao barramento permite o acesso às três interfaces do cluster usando, operações de entrada/saída mapeadas em memória.

O processo de configuração do cluster começa com o MR2 escrevendo dados no banco de registradores interno do *wrapper*. Após detectar uma operação de escrita nos registradores de configuração, o *wrapper* gera um pulso no sinal *config\_en*. Este mesmo procedimento é realizado para prover dados da rede para o cluster. Uma operação de escrita nos registradores destinados à transmissão de pacotes ao cluster gera pulsos nos sinais *take* e *is\_proto*. É importante salientar que não há necessidade de desativar os sinais de controle via software, sendo esta ação executada no hardware do *wrapper*.

Figura 20 – Interfaces e estrutura parcial do wrapper do cluster.

A implementação do SPP-NIDS descrita a partir da Seção 4.1.2, coleta os dados de ataques através de *polling* e não interrupções como descrito acima. O software do MR2 monitora a detecção de ataques e, quando um ataque é identificado, executa ações de tratamento deste. Após tais ações de tratamento serem iniciadas, o MR2 gera um pulso no sinal *int\_ack* a fim de liberar a unidade de controle do cluster.

#### 4.1.7 O módulo serial

O módulo serial é responsável por prover comunicação entre o usuário trabalhando em um computador hospedeiro e o sistema de detecção de intrusão. Esta comunicação é realizada via um protocolo serial padrão RS-232.

O computador hospedeiro é responsável por enviar: o software a ser executado pelo processador MR2, as regras às pico-CPUs, e os dados capturados na rede – caracteres a serem comparados. O computador hospedeiro recebe do sistema o número de ataques detectados e o número da regra de cada ataque para futura análise.

#### 4.1.8 O processador MR2

O processador que controla o cluster é chamado de MR2 [CAL04]. Ele é um processador Harvard de 32 bits que implementa parcialmente uma arquitetura do conjunto de instruções do processador MIPS 2000. O simulador SPIM [LAR05] é usado para validar o software que interage

com o cluster de pico-CPUs. O subconjunto de instruções do MIPS utilizado no MR2 aparece na Tabela 2.

| Tabela 2 – Instruc | cões do MR2. | um subconjunto | de instruções d | lo MIPS 2000 | [CAL04]. |

|--------------------|--------------|----------------|-----------------|--------------|----------|

|                    |              |                |                 |              |          |

| MR2 INSTRUCTIONS |                |       |                |

|------------------|----------------|-------|----------------|

| ADDU             | Rd, Rs, Rt     | SB    | Rt, Imed16(Rs) |

| SUBU             | Rd, Rs, Rt     | sw    | Rt, Imed16(Rs) |

| AND              | Rd, Rs, Rt     | SLT   | Rd, Rs, Rt     |

| OR               | Rd, Rs, Rt     | SLTU  | Rd, Rs, Rt     |

| XOR              | Rd, Rs, Rt     | SLTI  | Rt, Rs, Imed16 |

| SLL              | Rd, Rt, shamt  | SLTIU | Rt, Rs, Imed16 |

| SRL              | Rd, Rt, shamt  | BEQ   | Rs, Rt, label  |

| ADDIU            | Rt, Rs, Imed16 | BGEZ  | Rs, label      |

| ANDI             | Rt, Rs, Imed16 | BLEZ  | Rs, label      |

| ORI              | Rt, Rs, Imed16 | BNE   | Rs, Rt, label  |

| XORI             | Rt, Rs, Imed16 | J     | label          |

| LUI              | Rt, Imed16     | JALR  | Rs, Rd         |

| LBU              | Rt, Imed16(Rs) | JAL   | label          |

| LW               | Rt, Imed16(Rs) | JR    | Rs             |

#### 4.2 FORCE10 P-Series

O único produto comercial encontrado pelos Autores deste trabalho que se assemelha à arquitetura proposta neste Trabalho de Conclusão é a plataforma P-Series da empresa *Force10* [FOR06]. Esta arquitetura é baseada em uma tecnologia chamada de DPI (*Dynamic Parallel Inspection*), ou Inspeção Dinâmica e Paralela, que permite que milhares de regras sejam verificadas sobre cada byte de um pacote. O produto funciona como um firewall, baseado nas regras do Snort. Sua estrutura funciona como filtros no tráfego da rede, como mostrado na Figura 21.

Figura 21 - Modelo de filtros usado na plataforma P-Series.

Segundo a empresa, o produto possui suporte às seguintes aplicações:

- Detecção e prevenção de intrusão de redes à taxas de 1 e 10 Gbps;

- Assistência na inspeção e flexibilidade na captura de dados para aplicações de monitoramento eletrônico;

- Interface de aplicação aberta para segurança de rede personalizada e aplicações de monitoramento de rede.

As características da plataforma P-Series, conforme apresentadas pela empresa, são as seguintes:

- Inspeção de pacotes com suporte a *Jumbo frames*, em uma rede de até 10 Gbps;

- Desempenho previsível desconsiderando as condições de tráfego na rede ou número de regras;

- Suporte à dois modos de operação, um ativo na linha e outro passivo de monitoramento/captura;

- Escrita de regras dinamicamente direto no hardware, o que permite uma maior flexibilidade na resposta ao tráfego malicioso;

- Compatível com os softwares Snort, Bro, Ethereal e Tcpdump.

A Figura 22 mostra os produtos P1 e P10, ambos usando arquitetura da plataforma P-Series, da empresa Force10.

Figura 22 - Firewall P-Series, da empresa Force10.

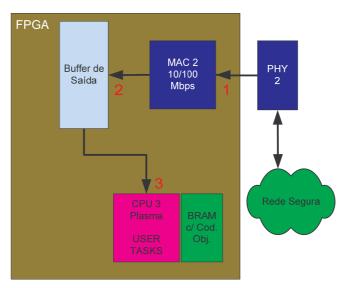

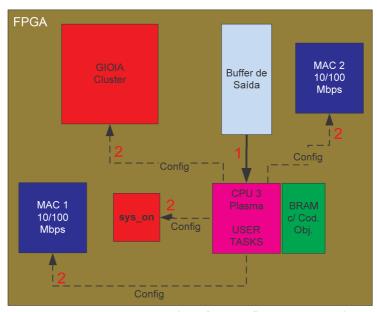

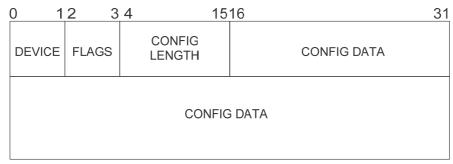

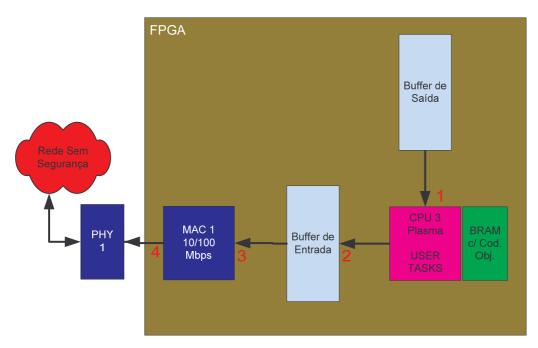

### 5 PrimeSec - Um NIDS em Hardware Multiprocessado