# Projeto para Prototipação de um IP Soft Core MAC Ethernet

Ney Laert Vilar Calazans<sup>1</sup>

Fernando Gehm Moraes<sup>1</sup>

Delfim Luiz Torok<sup>1</sup>

Andrey V. Andreoli<sup>1</sup>

Resumo: Este artigo descreve as estratégias de projeto e validação de um Núcleo de Propriedade Intelectual (IP soft core) destinado a desempenhar o papel de protocolo de Controle de Acesso ao Meio (MAC) para redes locais do tipo Ethernet. O projeto deste IP soft core foi completamente realizado na linguagem VHDL, sendo flexível, portável e personalizável para aplicações específicas. A implementação é especialmente desenvolvida para adaptar-se bem a ambientes onde o core reside em dispositivos de hardware reconfigurável tais como FPGAs baseados em RAM. Finalmente, o artigo introduz uma proposta para vários ambientes de validação do protótipo, com o objetivo de testar e caracterizar o IP soft core MAC Ethernet no escopo de redes locais reais.

¹ {calazans, moraes, torok}@inf.pucrs.br, andrey@penta.ufrgs.br Pontificia Universidade Católica do Rio Grande do Sul - PUCRS Faculdade de Informática – FACIN Av. Ipiranga, 6681 - Prédio 30 / BLOCO 4 CEP 90619-900 - Porto Alegre - RS - BRASIL

### 1 Introdução

Dentre as tecnologias de transmissão de dados em redes locais modernas (em inglês, *Local Area Networks* ou LANs), aquela conhecida como Ethernet é sem dúvida a mais difundida. Sua popularidade deriva de diversos fatores. Entre estes, salienta-se o fato de se tratar de padrão internacional reconhecido por diversos organismos internacionais (e.g. IEEE, ISO, ANSI) [4]. Outro motivo para sua difusão em escala mundial é que desde sua proposta original por Metcalfe e Boggs [6], as especificações e o direito de construir este tipo de interfaces de rede foram abertos. Esta abertura, combinada com a facilidade de uso e robustez do sistema, resultou no grande sucesso da tecnologia, entre outros no ramo de computadores. A maioria dos computadores pessoais atualmente comercializados estão equipados com uma interface 10-Mbps e/ou 100-Mbps Ethernet, possibilitando conectá-los facilmente a uma LAN preexistente. Outra vantagem relevante da tecnologia Ethernet é a escalabilidade da tecnologia, vinculada ao caminho evolutivo do padrão para velocidades de transmissão cada vez mais altas (10, 100 e 1Gbps) e compatibilidade a nível de meio físico de transmissão e equipamentos.

O presente trabalho descreve o projeto e a validação de parte da tecnologia Ethernet voltado para a implementação sobre dispositivos reconfiguráveis. Trata-se aqui da implementação do protocolo de acesso ao meio em redes Ethernet (Medium Access Control, ou MAC), que corresponde à camada do protocolo diretamente implementada em hardware digital. Tal implementação toma a forma de um módulo de Propriedade Intelectual reutilizável pré-validado e pré-caracterizado (em inglês, Intellectual Property core, ou IP core). O objetivo estratégico do trabalho foi dominar a tecnologia de implementação de controladores de redes locais, concentrando-se nos níveis inferiores de abstração (hardware e software básico mínimo). Endereçou-se a construção de módulos de hardware e software no nível de enlace do modelo de referência OSI da ISO. Os módulos funcionais implementação e comparação de dispositivos e protocolos de acesso ao meio para LANs.

## 1.1 Hardware reconfigurável

Muitas aplicações computacionais necessitam alteração frequente de sua funcionalidade ou grande flexibilidade de comportamento. Isto é atualmente possível não apenas via implementação em software, mas também em hardware, graças à existência de dispositivos de hardware reconfigurável.

No caso de implementações em software existe um hardware subjacente normalmente composto por um processador de conjunto de instruções (em inglês, *instruction set processor* ou ISP) associado a uma memória. ISPs podem ser programados para executar uma ou mais aplicações específicas preenchendo a memória de instruções com software que implementa as aplicações.

No caso de implementação em hardware, as aplicações flexíveis são obtidas principalmente através de uso de dispositivos tais como FPGAs [7]. De fato, os FPGAs modificaram a tradicional distinção entre hardware e software, visto que sua funcionalidade em hardware pode ser alterada de forma total ou parcial ou até mesmo dinâmica.

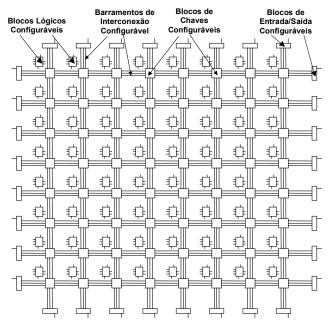

A arquitetura genérica de FPGAs, ilustrada pela Figura 1, consiste em uma matriz de elementos agrupados em *blocos lógicos* configuráveis, que podem ser interconectados, por *barramentos de interconexão* configuráveis. Semelhante a uma PAL (*Programmable Array Logic*), as interconexões entre os elementos são implementadas por *blocos de chaves* configuráveis pelo usuário. Através de *blocos de entrada/saída* configuráveis é realizado o interfaceamento com o mundo externo. Os FPGAs foram introduzidos em 1985 pela empresa Xilinx. Desde então, grande variedade de FPGAs foi desenvolvida por várias outras companhias, entre elas: Actel, Altera, Atmel, Plessey, Plus Logic, Advanced Micro Devices (AMD), Quicklogic, Algotronix, Concurrent Logic, e Crosspoint Solutions.

Figura 1. Arquitetura de um FPGA genérico.

## 1.2 Estrutura do artigo

Na Seção 2, são apresentados alguns conceitos básicos de redes de computadores e da tecnologia Ethernet, além de mostrar a arquitetura geral de um controlador de acesso a uma rede Ethernet via um estudo de caso de um circuito integrado comercial. A estrutura geral do IP core MAC Ethernet é tema da Seção 3, que propõe um diagrama de blocos para o sistema,

e apresenta o ambiente de uso do IP core proposto. A Seção 4 apresenta o detalhamento do projeto e sua validação, além de uma proposta de ambiente de teste a ser empregado na validação do IP core. Finalizando, a Seção 5 apresenta algumas conclusões parciais, relata o estado atual de andamento do trabalho e delineia trabalhos futuros no tema.

## 2 Redes de Computadores e o Padrão Ethernet

Uma rede de computadores é definida como um conjunto de módulos processadores capazes de trocar informações e compartilhar recursos interligados por um sistema de comunicações [9]. Uma rede local é aquela que apresenta seus módulos processadores interligados através um sistema de comunicação localizado numa área restrita. Atualmente, considera-se área restrita uma região delimitada por distâncias máximas entre 100 m e 25 Km [9]. Redes locais são ainda caracterizadas pela taxa de transmissão de bits associada. As distâncias e as taxas de bits atuais mais encontradas são 0.1 a 10 Km e 10 a 100 Mbps, respectivamente. O produto destes valores pode ser usado para definir os limites desta tecnologia, embora estes sejam mutáveis ao longo do tempo. Pode-se assim caracterizar redes locais como sendo aquelas com um vazão por limite de distância variando hoje em 1Mbps.m e 1Gbps.m [9]. Contudo, o limite superior vem sendo paulatinamente ultrapassado com novas tecnologias, tais como Fast Ethernet, ATM (Asynchronous Transfer Mode) e as Gigabit Ethernet. Redes locais adotam quase sempre estratégias baseadas no controle distribuído da comunicação, que oferece as vantagens de baixo custo de implementação e a descentralização. Esta descentralização traz vantagens como diminuição do processamento de informações de controle, e aumento da tolerância a falhas da rede.

Um *protocolo de comunicação* é um conjunto de regras que regem a comunicação entre módulos processadores mediante as conexões físicas que determinam uma *topologia de rede*. Uma *arquitetura de rede* é formada por níveis, interfaces e protocolos, e é definida como um conjunto de camadas hierárquicas, cada uma destas sendo construída utilizando as funções e serviços oferecidos pelas camadas inferiores [9].

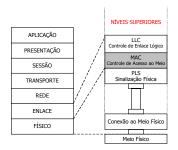

#### 2.1 Hierarquia de protocolos – o modelo de referência OSI

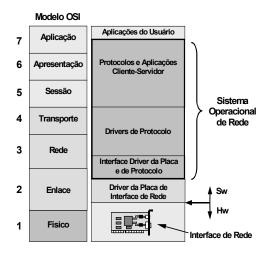

O modelo de referência para Interconexão de Sistemas Abertos (em inglês, *Reference Model for Open Systems Interconnection* ou OSI-RM), proposto pela International Standards Organization (ISO), permite a estratificação, o projeto e a implementação de protocolos padronizados em redes de comunicação. O OSI-RM divide o tratamento de informações de rede em sete níveis de abstração. A hierarquia proposta pelo OSI-RM é detalhada no lado esquerdo da Figura 2.

A IEEE (Institute of Electrical and Electronic Engineers) Standards Association definiu um padrão de redes locais a partir da tecnologia Ethernet original [6], identificando este padrão pelo código IEEE 802.3. Este ocupa o equivalente aos níveis 1 e 2 no OSI-RM. A nível de redes locais, o padrão 802.3 é o mais utilizado hoje.

Para que um módulo processador possa operar em uma rede de computadores, em geral devem ser instalados recursos de hardware e software que complementem seus dispositivos e o sistema operacional local.

Figura 2. O OSI-RM e um exemplo típico de sistema operacional de rede.

Em uma rede local, o hardware adicional a ser acrescentado ao módulo processador se constitui, em geral, de uma placa de interface de rede e um software, genericamente denominado sistema operacional de rede. Os componentes típicos de um sistema operacional de rede são mostrados na Figura 2 à direita, comparados com os níveis do OSI-RM. Tal sistema engloba um conjunto de módulos implementando os protocolos, as aplicações cliente-servidor de uso geral e um ou mais módulos de software básico (em inglês drivers). O controle e configuração da placa de rede são realizados pelo driver de dispositivo, que se comunica com o sistema operacional de rede através de uma interface bem definida.

#### 2.2 Estudo de caso de controladores de interface redes: o CS8900A

Um Controlador de Interface de Rede (em inglês, Network Interface Card ou NIC) é um hardware dedicado a fornecer serviços de envio de dados através de uma rede. Dados são convertidos em cadeias de bits e fracionados em pacotes, sendo a seguir enviados ao sistema de destino. Também é responsabilidade do NIC recompor, a partir dos pacotes recebidos, os dados originais. Freqüentemente, NICs ainda implementam um mecanismo de controle de fluxo e de erros para garantir a integridade dos dados contidos nos pacotes, estes últimos normalmente denominados quadros.

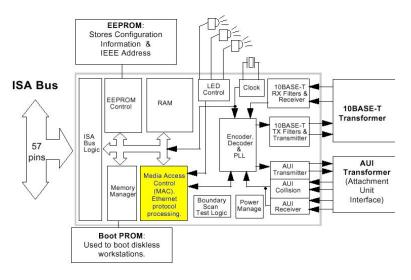

Existe hoje grande quantidade de circuitos integrados (CIs) comerciais que implementam a maior parte da funcionalidade de hardware de NICs Ethernet. A Figura 3 mostra o esquema geral de um NIC comercial usado em computadores pessoais. Ele é implementado com o CI CS8900A da empresa Cirrus Logic, Inc [2]. Este CI é instalado em uma placa com barramento padrão ISA. O controlador permite a conexão ao meio de transmissão diretamente (via par trançado, através do conector RJ-45) ou através do conector AUI a um transceptor externo.

Figura 3. Diagrama de blocos do NIC, detalhando a estrutura interna CS8900A.

O diagrama de blocos do NIC apresenta o detalhamento da estrutura interna do CI CS8900A. Este NIC incorpora uma memória de inicialização (Boot PROM) que possibilita sua utilização em computadores sem periféricos locais, tais como estações sem disco e/ou unidade de CD-ROM. Este CI incorpora todos os circuitos digitais e quase todos os analógicos necessários a implementar o NIC. Os principais blocos funcionais incluem uma interface de acesso direto ao barramento ISA, um IP core MAC 802.3, buffers de memória, gerenciadores de acesso a EEPROM e Boot PROM e um transceptor 10BASE-T e respectivos filtros e interface AUI.

#### 2.3 A tecnologia Ethernet e o padrão 802.3

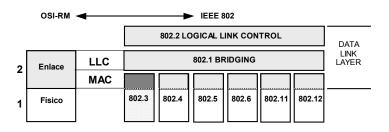

A tecnologia Ethernet foi projetada para transferência de dados limitada a pequenas distâncias. Ela baseou-se originalmente no protocolo Carrier Sense Multiple Access with Collision Detection (CSMA-CD). A Figura 4 apresenta a relação entre os principais padrões IEEE 802 e o OSI-RM. Conforme ilustrado, o padrão 802.2 especifica a compatibilidade

com o nível 2 do OSI-RM, enquanto que 802.3 a 802.12 referem-se também ao nível 1 do OSI-RM. O protocolo de acesso ao meio baseado no CSMA/CD é batizado pela IEEE sob o número IEEE 802.3. Os padrões 802.4 e 802.5 consistem na especificação do protocolo tipo passagem de permissão, implementado em barramento (*token bus*) e em anel (*token ring*), respectivamente. O padrão 802.6 define um padrão para transporte de dados a alta velocidade em regiões metropolitanas e é chamado de *Distributed Queue Dual Bus* (DQDB) [9].

Figura 4. Relação entre os padrões IEEE 802 e o OSI-RM.

Recentemente, dois novos padrões foram definidos para especificação de novas tecnologias de rede. Um é o padrão IEEE 802.11, que especifica as camadas *MAC* (Medium Access Control) e *PHY* (Physical Layer) para redes locais sem fios (em inglês, *wireless*). O propósito deste padrão é prover a conexão sem fios para equipamentos ou estações móveis, dentro de uma área local, que podem ser equipamentos portáteis ou instalados em veículos. Este padrão também especifica o acesso ao meio para as bandas de freqüência utilizadas na comunicação dentro da área local. Outro é o padrão IEEE 802.12 (conhecido em inglês por *Demand Priority Access Method, Physical Layer and Repeater Specifcations*), que surgiu de uma proposta das empresas AT&T, IBM e HP denominada de *100VG-AnyLAN*. Esta proposta está baseada em uma topologia de rede em *estrela* com método de acesso por contenção, onde a comunicação é realizada por meio de um dispositivo denominado *HUB* (concentrador). As estações só podem transmitir quando o HUB concede a permissão. Este padrão especifica redes de alta velocidade, tipicamente 100Mbps, com suporte a diferentes tecnologias de acesso ao meio, Ethernet e Token Ring/Bus, no mesmo ambiente de rede.

O método de acesso ao meio CSMA/CD pertence ao subnível de controle de acesso ao meio (MAC) [4]. O subnível MAC e o controle de enlace lógico (LLC - Logical Link Control) juntos englobam a funcionalidade necessária para o nível de enlace definido no modelo OSI. Os níveis físico e de enlace dados pelos padrões IEEE 802.2 e 802.3 correspondem aos níveis mais baixos do OSI/ISO conforme ilustra a Figura 5.

Figura 5. O Padrão IEEE 802.3 e sua relação com o modelo referência OSI.

### 2.4 Quadros Ethernet e o protocolo CSMA/CD

A Figura 6 detalha o formato de quadro usado na transmissão de dados via tecnologia Ethernet. Um padrão anterior, Ethernet II DIX, ainda em uso por alguns fabricantes, emprega um quadro ligeiramente distinto. A diferença está no campo de tamanho, sombreado na Figura 6. Existem formas de compatibilizar transmissão e recepção entre estes [10].

#### Quadro 802.3 Básico

| Preâmbulo<br>7 bytes | Delimitador de Início de Quadro (SFD) 6 byt | no Fonte | Tamanho<br>do<br>quadro<br>2 bytes | Dados<br>46 – 1.500 bytes | FCS<br>(CRC)<br>4 bytes |

|----------------------|---------------------------------------------|----------|------------------------------------|---------------------------|-------------------------|

|----------------------|---------------------------------------------|----------|------------------------------------|---------------------------|-------------------------|

Figura 6. Estrutura do quadro IEEE 802.3 básico.

A natureza das informações contidas em cada um dos campos do quadro padrão 802.3 são em sua maioria óbvias a partir da Figura 6. No quadro Ethernet, todos os campos são de tamanho fixo, menos o de dados, que deve conter um número inteiro de bytes. O quadro Ethernet é definido como não válido quando um quadro não possuir um número inteiro de bytes, ou se as partes de um quadro recebido não gerarem um valor de CRC idêntico ao CRC recebido, ou se o tamanho do quadro for menor que o tamanho mínimo.

Para que os quadros Ethernet sejam adequadamente transmitidos ou recebidos, o subnível MAC deve desempenhar diversas tarefas, visando garantir a transmissão dos dados com integridade. Na transmissão de quadros, o MAC aceita dados do subnível LLC e monta um quadro. A seguir, transmite um fluxo de dados serial para o nível físico. Sempre que o meio físico está ocupado, o MAC adia a transmissão de dados. O MAC também calcula e acrescenta o FCS para os quadros de saída, e verifica o alinhamento de byte completo. Para garantir o intervalo de tempo mínimo entre quadros, o MAC retarda a transmissão dos dados por um período adequado. Ele também é responsável por detectar colisões e reter a

transmissão quando isto ocorre. Após uma colisão, o MAC reforça esta por algum tempo, para garantir a detecção por toda a rede, e programa a retransmissão depois de uma colisão para um instante futuro calculado. Finalmente, o MAC acrescenta preâmbulo, delimitador de início de quadro e FCS, para todos quadros de saída. Por outro lado, na recepção, o MAC verifica erros de transmissão nos quadros recebidos por meio do FCS e verifica o alinhamento de byte completo. Também descarta quadros menores que o mínimo, os que possuem erros de CRC e aqueles que não têm número inteiro de bytes. O MAC ainda remove o preâmbulo, o delimitador de início de quadro e o FCS de todos quadros recebidos. Finalmente, o MAC transfere a informação útil do quadro ao módulo processador.

#### 3 Estrutura e Ambiente de uso de NICs Ethernet sobre FPGAs

O projeto de dispositivos de transmissão de dados de alto desempenho e dispositivos reconfiguráveis são áreas de pesquisa em crescente desenvolvimento. O objetivo específico deste trabalho foi implementar um módulo de hardware *reutilizável* e *portável* para diferentes tecnologias de implementação, junto com o software mínimo necessário ao seu uso. Outro objetivo é que o módulo desenvolvido permita a rápida construção de sistemas digitais que empreguem o padrão de comunicação IEEE 802.3. Uma das medidas mais importantes no sentido de tornar o hardware portável e reutilizável foi a escolha da linguagem VHDL [5], em tese independente da tecnologia de implementação.

As justificativas para empreender o presente trabalho, malgrado a disponibilidade de circuitos integrados (CIs) comerciais que desempenhem a função de controle de acesso ao meio Ethernet, são múltiplas. Além dos beneficios acadêmicos de dominar uma tecnologia estratégica de transmissão de dados, existem beneficios potenciais para empresas usuárias da tecnologia Ethernet. O custo de CIs controladores para Ethernet é relativamente alto. Além disso, os CIs comerciais são inflexíveis quanto às funções que podem desempenhar, ou seja, funções a mais não podem ser acrescentadas, exceto pala adição de outros CIs ao sistema, e funções desnecessárias presentes no CI não podem deste ser removidas. O desenvolvimento de um IP core MAC Ethernet em VHDL, aliado ao emprego de dispositivos reconfiguráveis de baixo custo, remove esta inflexibilidade, permitindo adaptar o hardware ao subconjunto de funções estritamente necessárias no produto que o emprega, melhorando a relação custo beneficio de produtos tecnológicos. O acesso à tecnologia de implementação de IP cores Ethernet permite liberar empresas da necessidade de importar CIs, muitas vezes a um custo que reduz a competitividade de seus produtos. Outra justificativa, ainda no mesmo sentido é a perspectiva de se ver em breve o emprego de controladores de rede de baixo custo agregados a produtos de consumo, tais como eletrodomésticos, viabilizando aplicações de automação de lares e de escritórios.

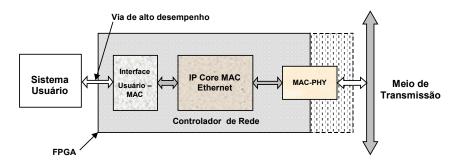

#### 3.1 Arquitetura do hardware

A Figura 7 mostra o diagrama de blocos do sistema computacional em implementação e o ambiente onde o mesmo está inserido. Este diagrama ilustra no interior do retângulo

sombreado o conteúdo do FPGA onde é implementado o IP core. São dois módulos principais: a Interface Usuário-MAC e o IP core MAC Ethernet. O primeiro módulo interliga o computador hospedeiro ao segundo módulo. O Ip core MAC Ethernet, por sua vez, comunica-se por um lado com o módulo Interface Usuário-MAC e, por outro com uma interface com o meio físico, denominada MAC-PHY.

Figura 7. Diagrama de blocos do IP core em desenvolvimento e do ambiente típico de seu emprego.

A conexão ao meio de transmissão é realizada através de uma interface PHY universal para o protocolo Ethernet, com suporte para taxas de transmissão 10Mbps e 100Mbps. Esta interface executa a tarefa de detectar colisões, capturar dados trafegando na rede, sincronização da recepção e transmissão, bem como a adaptação do sinal elétrico dos quadros Ethernet para e de valores de tensão adequados à transmissão no meio físico. Uma pequena parte desta interface está dentro do FPGA (a que adapta o IP core MAC Ethernet ao circuito específico do nível físico que se pretende empregar), enquanto que a maior parte deste está em circuito externo.

A implementação de hardware usa plataformas de prototipação comerciais. Empregam-se ferramentas para desenvolvimento de circuitos digitais (sistemas de projeto auxiliado por computador, em inglês, *Computer Aided Design* ou CAD) para descrição, análise, síntese lógica e síntese física. Assume-se que a comunicação entre o NIC em desenvolvimento e o sistema usuário se dá através da via de alto desempenho. Tipicamente, esta via de acesso é composta por um barramento local padronizado de alto desempenho, tal como o PCI Local Bus [8].

As placas de prototipação em uso ao longo deste trabalho são a XSV800 [12] e a HOT Development System XL (HOT2-XL) [11], das empresas Xess Inc. e Virtual Computer Corporation (VCC), respectivamente. O software de desenvolvimento do hardware é o sistema de CAD Foundation da Xilinx [13], complementado pelo simulador Active-HDL da empresa Aldec, Inc. Para validação dos protótipos emprega-se, além de placas de prototipação e osciloscópio, ferramentas avançadas tais como analisadores lógico e de protocolo Ethernet.

## 4 Projeto e Validação do IP core MAC Ethernet

A implementação do IP core foi dividida em duas partes principais, a interface com a *Via de Alto Desempenho* e a segunda é o IP core de controle de acesso à rede. Estritamente falando, apenas a segunda parte constitui o trabalho endereçado aqui. Contudo a validação do IP core em questão exige a construção de um módulo para desempenhar o papel da primeira parte, ainda que de forma parcial.

#### 4.1 Ambiente de implementação/validação do IP core

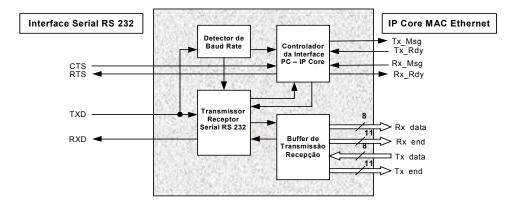

O diagrama de blocos da Figura 7 discutido na Seção 3.1 é bastante geral. Este diagrama supõe paralelismo no processamento, com a conexão intra-módulos do hardware reconfigurável sendo do tipo fortemente acoplada (via barramento local de alto desempenho). No início do desenvolvimento deste trabalho, não se dispunha de uma plataforma de prototipação dotada de barramento PCI ou outro barramento de desempenho razoável. Logo, utilizou-se uma linha de comunicação serial RS-232 disponível na plataforma XSV800, então em uso. Atualmente, o módulo de interface está sendo adaptado a interagir com um IP core PCI, já disponível em nova plataforma (HOT2-XL).

Representado na Figura 8 tem-se o diagrama de blocos da Interface Usuário-MAC, com a função de operacionalizar a transferência de dados, recebendo e transmitindo quadros Ethernet via interface serial RS-232 de e para um computador pessoal, desempenhando papel de um dispositivo usuário genérico. Problemas de compatibilidade de velocidade surgem apenas no momento de validar a recepção de pacotes em tempo real, caso a taxa de chegada destes exceda a capacidade de armazenamento local. Para fins de teste inicial de transmissão e recepção com taxas de chegada de pacotes limitada o ambiente atual é perfeitamente adequado.

Figura 8. Diagrama de blocos da Interface Usuário-MAC.

Internamente, a Interface Usuário-MAC envia e recebe dados do IP core MAC Ethernet de forma paralela, por meio de um barramento. A interface Usuário-MAC pode ser dividida em quatro módulos, conforme representado na Figura 8. O primeiro é um Transmissor/Receptor serial RS-232, responsável pela comunicação com o computador hospedeiro. O segundo módulo, Detetor de Baud Rate, é utilizado apenas no início do envio de dados do hospedeiro, para detectar a taxa de transferência com que os dados são transmitidos e automaticamente adaptar a velocidade de recepção/transmissão de dados. O terceiro módulo, Controlador da Interface PC-IP core, realiza a sincronização da transferência dos dados entre o computador pessoal e o IP core MAC Ethernet. Para isto, ele utiliza o quarto módulo, Buffer de Transmissão Recepção, que desempenha a função de memória intermediária. O Buffer de Transmissão Recepção se conecta a dois barramentos de 8 bits, um para a transferência dos dados (Rx\_data) ao IP core MAC Ethernet, e o outro para transferir os dados recebidos (Tx\_data) do IP core MAC Ethernet para o hospedeiro. Esta interface está atualmente sendo substituída por conexão com uma interface de alto desempenho, o IP core PCI proposto em [1].

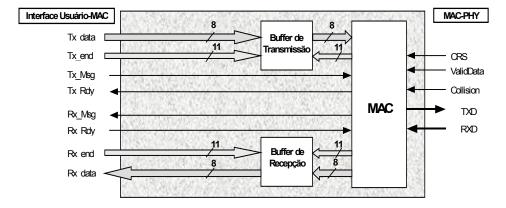

#### 4.2 IP core MAC Ethernet

A comunicação Interface Usuário-MAC/IP core MAC Ethernet se faz através de buffers com capacidade para uma mensagem de tamanho máximo (1500 bytes). Estes buffers são implementados mediante o uso de memórias de dupla porta internas ao FPGA da plataforma XSV800. O IP core MAC Ethernet, por sua vez, utiliza os buffers para receber e transferir quadros Ethernet em conformidade com o protocolo MAC. O IP core realiza a transferência dos dados de e para o meio físico utilizando-se de a interface MAC-PHY definida anteriormente, na Seção 3.

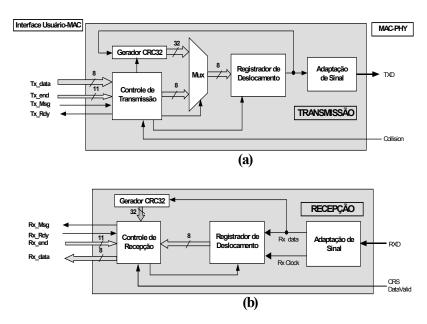

Figura 9. Diagrama de blocos do IP core MAC Ethernet.

O IP core MAC Ethernet é representado na Figura 9. Ele possui três módulos que em conjunto implementam o controle de acesso ao meio. Existem dois buffers, um para a recepção e outro para a transmissão dos quadros Ethernet, sob controle do módulo denominado MAC. Este último se conecta ao módulo MAC-PHY que é, em sua maior parte, externo ao protótipo em desenvolvimento.

#### 4.3 Módulo MAC

O Módulo MAC implementa o método CSMA/CD de acesso ao meio do padrão IEEE 802.3 10BASE-T. Este controla todos os aspectos de transmissão e recepção dos quadros Ethernet e inclui: tratamento de colisão, geração de preâmbulo, detecção e geração de CRC e modo teste. O MAC também possui características programáveis, que incluem controle de retransmissão automática em colisão, e do complemento automático de tamanho mínimo de quadros transmitidos (bits de enchimento, ou *padding*). O MAC, conforme ilustra a Figura 10, é fisicamente dividido em duas partes, que executam suas funções de forma independente.

Figura 10. Diagrama de blocos do módulo MAC, detalhando Transmissor e Receptor.

A transmissão do quadro acontece em duas fases. Na primeira fase, a Interface Usuário-MAC armazena no Buffer de Transmissão a mensagem recebida do hospedeiro. A primeira fase inicia quando a Interface Usuário-MAC emite um comando de transmissão

(sinal Tx\_Msg). Isto informa ao Controle de Transmissão, representado na Figura 10(a), que uma mensagem está pronta no buffer para ser transmitida. Na segunda fase, o Controle de Transmissão converte a mensagem armazenada no buffer em um quadro padrão Ethernet. Isto se faz transmitindo de forma serial, para o Adaptador de Sinal o quadro. Este último é responsável por realizar tarefas tais como serialização/desserialização dos dados, adaptando a largura de dados dos módulos MAC e PHY. A segunda fase inicia-se com o MAC transmitindo o preâmbulo e o delimitador de início de quadro (SFD). O Preâmbulo e o SFD são seguidos pelo Endereço Destino, Endereço Fonte, Tamanho do Quadro e o campo de Dados, conforme a estrutura do quadro básico da Figura 6. Se o quadro for menor que 64 bytes, o Controle de Transmissão complementa o campo de dados para atingir o tamanho mínimo, com bits de enchimento. Finalmente, acrescenta-se um CRC de 32 bits, calculado pelo algoritmo previsto no padrão [4]. A seguir, a transmissão encerra-se, e isto é informado, via o sinal Tx\_Rdy, à Interface Usuário-MAC.

Semelhante à transmissão, a recepção de quadros acontece em duas fases. Na primeira fase, o Controle de Recepção, representado na Figura 10(b), recebe um quadro Ethernet armazenando no buffer de Recepção. A primeira fase de recepção começa com a chegada do quadro, proveniente do PHY. Este é tratado pelo Adaptador de Sinal, escrevendo a seqüência de bits do quadro recebido no Registrador de Deslocamento. Este, por sua vez, é usado para converter a seqüência de bits, do formato serial para o paralelo. O Controle de Recepção remove o Preâmbulo e o SFD e então analisa o Endereço Destino. Se o Endereço Destino do quadro confere com o critério e valores programados no filtro de endereço do Controle de Recepção, o pacote é armazenado no buffer de Recepção. O CRC é então conferido, e o Controle de Recepção informa (via sinais de erro não mostrados na Figura) à Interface Usuário-MAC se um quadro válido foi recebido ou não. Na segunda fase, a Interface Usuário-MAC transfere o quadro recebido até o hospedeiro.

Neste ponto, é importante considerar que a taxa de transferência de dados a ser utilizada na interface serial é no máximo da ordem de 115,2 Kbps. Esta taxa, comparada com a velocidade do IP core, padronizada em 10 Mbps, apresenta a interface serial como um gargalo. O gargalo impede a transmissão e recepção de quadros em intervalos de tempo menores que 5,0 ms, tendo em vista que no melhor caso este é o tempo calculado para um quadro de tamanho mínimo (72 bytes, do Preâmbulo até o FCS). Esta situação não representa o tráfego normal de uma rede local, cuja a temporização entre quadros (Inter Packet Gap – IPG) chega a um mínimo de 9,6 µs [4]. Entretanto, para testes do protótipo em desenvolvimento a transmissão dos quadros está sendo realizada de forma individual e o tempo entre quadros é devidamente aumentado para valores adequados ao gargalo da interface serial.

### 4.4 Validação do IP core MAC Ethernet

O processo de validação do IP core MAC Ethernet é assaz complexo. Nesta Seção apresenta-se apenas a forma geral do processo de simulação, sem preocupação com uma

cobertura extensa de todos os casos do algoritmo executado pelo MAC. Uma descrição mais detalhada do processo de validação encontra-se no Capítulo 5 de [14].

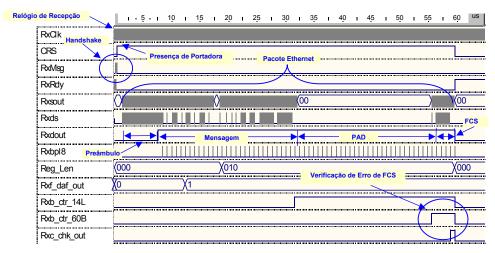

A Figura 11 mostra um exemplo de simulação completa da recepção de um pacote Ethernet de tamanho mínimo. Neste diagrama de tempos pode-se observar que aproximadamente a metade do pacote (30 bytes de um total de 64 bytes) possui bits de enchimento (*padding*), os quais serão removidos juntamente com o preâmbulo, SFD e FCS, para que somente a mensagem seja armazenada no buffer de recepção. Os sinais de controle e as diferentes fases do processo de recepção representadas neste diagrama de tempos, são a seguir detalhados.

O sinal Rxdout, quando é ativado, sinaliza, o término do SFD e o correspondente início do quadro (primeiro bit do campo de Endereço de Destino). Este sinal é gerado pelo bloco detetor de SFD, que é habilitado pelo controlador ao executar o handshake e detectar a presença de portadora via sinal CRS. O padrão irregular de bits mostrado no sinal Rxds mostra a parte inicial do quadro, incluindo os dados enviados. O círculo no canto inferior direito da Figura 11 marca o momento da recepção seguido de verificação do campo FCS. O sinal Rxds possui uma região sombreada no final do diagrama de tempos, mostrando a recepção do FCS da mensagem. Deve-se notar que a verificação do campo FCS está superposta com a recepção.

Figura 11. Diagrama de tempos da recepção completa de um pacote Ethernet de tamanho mínimo.

Para fins de estimativa de dimensões do IP core MAC Ethernet apenas, foi feita uma síntese física do controlador Ethernet completo conforme descrito na Figura 7. Acredita-se que o resultado final do controlador totalmente validado estará muito próximo destes valores, dado o avançado estado do processo de validação. Encontrou-se uma área equivalente a cerca de 110.000 portas lógicas (estimadas pela ferramenta de síntese Foundation M1 V3.3 da Xilinx), onde aproximadamente 59.000 portas correspondem aos módulos Interface

Usuário-MAC, a parte MAC-PHY do FPGA e ao módulo MAC sem os buffers de mensagem. Os dois buffers de mensagem consomem as restantes 51.000 portas equivalentes. A descrição completa corresponde a aproximadamente 4.000 linhas de código VHDL, sem contabilizar os arquivos de teste (todos os testbenches foram igualmente escritos em VHDL).

#### 4.5 Proposta de Plataformas de Experimentação

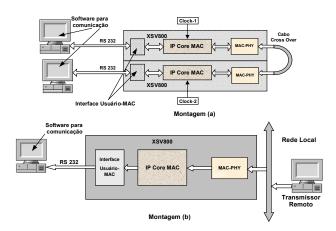

Propõe-se quatro tipos de experimentos a usar na validação do hardware do IP core MAC Ethernet. Detalha-se aqui a estrutura geral das montagens destes experimentos. Primeiro, para implementar e validar o protótipo duplica-se o IP core MAC Ethernet, criando uma Montagem (a). Como ilustrado na Figura 12(a), dois IP cores são configurados em duas plataformas de prototipação XSV800, de forma a emular a comunicação entre dois nós de rede.

**Figura 12**. Duas montagens de validação do protótipo do IP core MAC Ethernet. (a) Valida transmissão e recepção internamente ao projeto. (b) Valida recepção em rede local real com estação remota transmitindo quadros para o protótipo com grande espaçamento entre estes.

Na Montagem (a), nota-se que os clocks das duas instâncias do Core são independentes (Clock-1 e Clock-2). Isto evita que o teste seja viciado pelo uso de sinais de relógio em fase dos dois lados da comunicação, algo que não ocorre na realidade da comunicação entre módulos processadores empregando tecnologia Ethernet. A Montagem (a) possibilita validar a transmissão e recepção de quadros Ethernet de forma individual e isolada, evitando-se o risco de realizar testes numa rede local real, quais sejam, interferências indesejadas em outros nós da rede e funcionamento incorreto do protocolo devido a falhas no protótipo.

A Montagem (b) está representada na Figura 12(b). Ela consiste em configurar um IP core MAC Ethernet no FPGA da XSV800, funcionando apenas para recepção, mas

conectado a uma rede local real. Nesta configuração, o IP core é programado para a recepção de quadros Ethernet provenientes de uma rede real. Estes são enviados de um transmissor remoto conectado à rede local. Os quadros de teste devem ter o Endereço Destino (coincidente com o endereço MAC do IP core do protótipo) selecionado para evitar conflitos com o tráfego da rede local real. O tempo entre os quadros de teste é mantido em valores adequados à taxa de transferência da interface serial. Com a Montagem (b) valida-se o módulo receptor do IP core no que concerne o Controle de Recepção e o verificador de CRC.

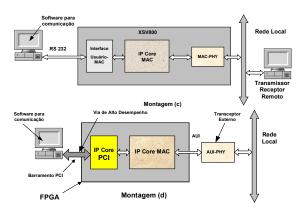

A Montagem (c), representada na Figura 13(c), implementa o IP core em uma configuração completa, possibilitando transmitir e receber quadros padronizados simultaneamente em uma rede local real, mantidos os mesmos cuidados com o endereçamento e o tempo entre os quadros da Montagem (b). A Montagem (d), mostrada na Figura 13(d), possibilita o uso uma via de alto desempenho (PCI) *de facto*. Esta plataforma é implementada sobre a placa HOT2-XL. Na Montagem (d), utiliza-se um IP core PCI, seja o disponível na plataforma HOT2-XL em si, seja o proposto em [1]. Um problema desta abordagem é que o IP core MAC Ethernet deverá ser modificado, uma vez que o FPGA da placa HOT2-XL (XC4062XL da Xilinx) não possui módulos internos de memória como o da placa XSV800 para dar suporte à implementação eficiente dos buffers de transmissão e recepção. Duas soluções são possíveis: implementar os buffers internamente no XC4062XL, a um alto custo de área, ou usar as memórias externas da placa HOT2-XL, tornando o core mais portável e menos auto-contido. Além disto, a plataforma HOT2-XL não possui um circuito que implemente o nível físico Ethernet. Logo, será necessário usar um transceptor AUI externo.

Figura 13. Duas outras montagens de validação do protótipo do IP core MAC Ethernet. (c) Valida transmissão e recepção em rede local real com estação remota transmitindo quadros para o protótipo com grande espaçamento entre estes. (d) Plataforma com IP core MAC Ethernet combinado com IP core PCI para implementar via de alto desempenho.

### 5 Conclusões e Trabalhos Futuros

Apresentou-se neste trabalho algumas das estratégias de projeto e validação de um IP soft core para a camada MAC de redes locais do tipo Ethernet.

O projeto e a validação funcional estão concluídos, enquanto que a prototipação e a validação física dos módulos encontra-se em andamento. Já existe um módulo funcional, projetado, construído e testado que implementa a Interface Usuário-MAC, bem como o software do lado do módulo processador que interage com esta interface. O transmissor de pacotes do IP core MAC Ethernet encontra-se projetado e validado a nível funcional, estando atualmente em fase de validação o seu protótipo em hardware. As plataformas de experimentação encontram-se em fase de teste, sendo que as Montagens (a), (b) e (c) estão disponíveis. A fase mais complexa do trabalho consistirá na adaptação do soft core para funcionamento acoplado a um soft core PCI. Esta tarefa envolve a transmissão em alta velocidade dos pacotes recebidos ao módulo processador, implicando o domínio de funções tais como acesso direto à memória do módulo processador (DMA) e transmissão de dados em rajada.

Um trabalho recente menciona a realização de parte das tarefas previstas no presente trabalho, aquele de Fragoso e outros em [3]. Algumas diferenças marcantes existem entre o presente trabalho e aquele. Em [3], os autores empregaram uma abordagem mista de implementação, usando edição de esquemáticos, macro módulos Altera e VHDL em diferentes partes da implementação. Isto eventualmente pode conduzir a uma implementação eficiente, mas que certamente será menos flexível que a descrita aqui, e mais vinculada a uma dada tecnologia, reduzindo a portabilidade do projeto. Segundo, o trabalho descrito em [3] limitou-se a uma implementação funcional a nível de simulação, sem uma realização hardware.

Alguns trabalhos são uma seqüência lógica do presente. O primeiro e mais relevante entre todos é a implementação de outras variedades de IP soft cores MAC para o padrão Ethernet, sobretudo Fast Ethernet, onde a velocidade de transmissão decuplicada (de 10Mbps a 100Mbps) coloca uma série de restrições de temporização pesadas no projeto. Estas restrições são bem mais difíceis de satisfazer que as do presente trabalho, sobretudo se a tecnologia alvo de implementação for a de FPGAs de baixo custo. Uma segunda variedade de core MAC de altíssimo interesse é o de redes locais sem fio (em inglês, *wireless*), dada a atual tendência de emprego de equipamentos portáteis, bem como o uso de transmissão de dados sem fio, via infra vermelho ou radiofreqüências. Aqui, a preocupação maior será o consumo de potência do hardware, muito mais que atender suas restrições de temporização.

### Agradecimentos

O autor Fernando Gehm Moraes agradece o suporte do CNPq (projeto integrado número 522939/96-1) e da FAPERGS (projeto número 96/50369-5). O autor Ney Laert Vilar

Calazans agradece o suporte do CNPq (projeto integrado número 520091/96-5) e da FAPERGS (projeto número 99/1555-3).

### Referências

- E. A. Cappelatti, F. G. Moraes, N. L. V. Calazans, L. A. Oliveira. "Barramento de Alto Desempenho para Interação Hardware/Software". VII Workshop Iberchip, IWS'2001, Março, 2001

- [2] Cirrus Logic, Inc. "CS8900A Cristal LAN<sup>TM</sup> ISA Ethernet Controller". Product Data Sheet, 1999. (Manual disponível em <a href="http://www.cirrus.com">http://www.cirrus.com</a>).

- [3] J. L. Fragoso, E. Costa, J. Rochol, S. Bampi, and R. Reis. "Specification and Design of an Ethernet Interface Soft IP". Journal of the Brazilian Computer Society, vol. 6, no. 3, April, 2000.

- [4] Institute of Electrical and Electronic Engineers. "IEEE Std 802.3, 2000 Edition". Standard document, 2000.

- [5] S. Mazor and P. Langstraat. "A guide to VDHL". Kluwer Academic Publishers. Massachusetts, 1992.

- [6] R. M. Metcalfe and D. R. Boggs, Ethernet: Distributed Packet Switching for Local Computer Networks. *Communications of the ACM*, Vol. 19, No. 5, pp. 395 404, July 1976. (Disponível em http://www.acm.org/classics/apr96/).

- [7] J. Rose and A. Sangiovanni-Vincentelli. Architecture of Field-Programmable Gate Arrays. Proceedings of the IEEE, vol. 81 no. 7, July, 1993.

- [8] T. Shanley and D. Anderson. "PCI System Architecture". Addison-Wesley Publishing Company. PC System Architecture Series. 787 pages. 4th edition, June, 1999.

- [9] L. F. G. Soares, G. Lemos e S. Colcher. "Redes de computadores: das LANs, MANs e WANs às Redes ATM". 2ª Edição. Editora Campus, Rio de Janeiro, 1995.

- [10] C. E. Spurgeon. "Ethernet: the definitive guide". O'Reilly and Associates, Inc., February, 2000.

- [11] Virtual Computer Corporation. "H.O.T. II & Hardware Object Technology". Virtual Computer Corporation. 1998. (Disponível em <a href="http://www.vcc.com">http://www.vcc.com</a>).

- [12] Xess Inc. "XSV Board V1.0 Manual". Platform Manual. 2000. (Disponível em http://www.xess.com).

- [13] Xilinx Corporation, Inc. "1999 Xilinx Data Book". 1999. (Disponível em http://www.xilinx.com/partinfo/databook.htm).

- [14] D. L. Torok. "Projeto Visando a Prototipação do Protocolo de Acesso ao Meio em Redes Ethernet". Dissertação de Mestrado, PPGCC-PUCRS, Agosto, 2001.